The move to 48 volts in transportation

The move from 12 and 24 volts to 48 volts is reshaping how companies approach mobility and robotics. It's a clear signal that the industry’s raising the bar for what’s possible in terms of performance and safety.

Read More

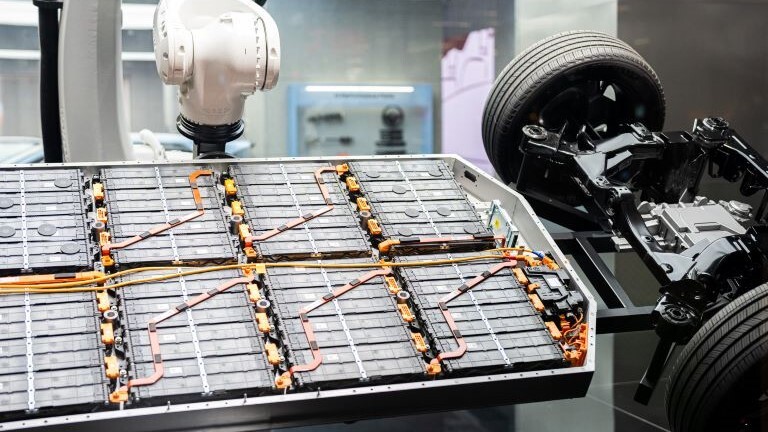

Key factors impacting autonomous transportation

Transportation covers more than personal vehicles, and autonomy will change society beyond self-driving cars. A small number of factors have a big impact on this widespread change. The largest opportunities are driving developments.

Read More

ECUs in off-highway vehicles

Off-highway vehicles are becoming power-user for electronic control units (ECUs). Manufacturers are adopting new system architectures that support more complex software features, driving efficiency and productivity.

Read More

System-level considerations for EVSE design

To get the optimum return over the EVSE’s lifetime, it is critical to evaluate the fundamental requirements of any specific charging station based on its purpose and location. These requirements may not always be the same.

Read More