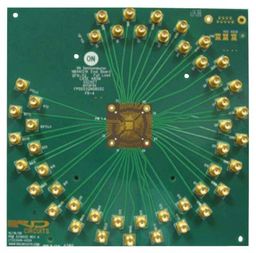

NB4N121KMNGEVB

Evaluation Board For NB4N121KMN Clock Differential Input Fan Out Distribution

- RoHS 10 Compliant

- Tariff Charges

The NB4N121K is a Clock differential input fanout distribution 1 to 21 HCSL level differential outputs, optimized for ultra low propagation delay variation. The NB4N121K is designed with HCSL clock distribution for FBDIMM applications in mind. Inputs can accept differential LVPECL, CML, or LVDS levels. Single-ended LVPECL, CML, LVCMOS or LVTTL levels are accepted with the proper VREFAC supply. Clock input pins incorporate an internal 50 ohm on die termination resistors.

- Typical Input Clock Frequency 100, 133, 166, 200, 266, 333 and400 MHz

- <1 ps RMS Additive Clock jitter

- Operating Range: VCC = 3.0 V to 3.6 V with VEE = 0 V

- 340 ps Typical Rise and Fall Times

- 800 ps Typical Propagation Delay tPD 100 ps Maximum Propagation

- Delta tPD 100 ps Maximum Propagation Delay Variation Per Each Differential Pair

- Differential HCSL Output Level (700 mV Peak-to-Peak)

Technical Attributes

Find Similar Parts

| Description | Value | |

|---|---|---|

| Clock and Timing Tools | ||

| Clock and Timing Tools |

ECCN / UNSPSC / COO

| Description | Value |

|---|---|

| Country of Origin: | NO RECOVERY FEE |

| ECCN: | EAR99 |

| HTSN: | 8471500150 |

| Schedule B: | 8471500150 |