S80KS5122GABHB020

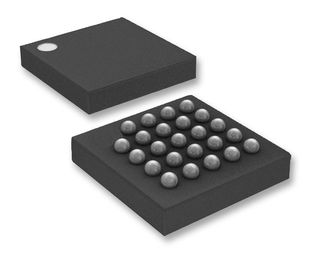

DRAM Chip DDR SDRAM 512Mbit 64M X 8 1.8V 24-Pin FBGA Tray

S80KS5122GABHB020 is a HYPERRAM™ self-refresh dynamic RAM (DRAM) with HYPERBUS™ interface. The DRAM array uses dynamic cells that require periodic refresh. Refresh control logic within the device manages the refresh operations on the DRAM array when the memory is not being actively read or written by the HYPERBUS™ interface host. Since the host is not required to manage any refresh operations, the DRAM array appears to the host as though the memory uses static cells that retain data without refresh. Hence, the memory is more accurately described as pseudo-static RAM(PSRAM). Since the DRAM cells cannot be refreshed during a read or write transaction, there is a requirement that the host limit read or write burst transfer lengths to allow internal logic refresh operations when they are needed. The host must confine the duration of transactions and allow additional initial access latency at the beginning of a new transaction, if the memory indicates a refresh operation is needed.

- 1.8V interface support, single-ended clock (CK) - 11 bus signals

- Bidirectional read-write data strobe (RWDS), output during read transactions as read data strobe

- Output at the start of all transactions to indicate refresh latency

- Input during write transactions as write data mask

- 200MHz maximum clock rate

- Maximum access time (tACC) is 35ns

- VCC power supply range from 1.7 to 2V

- 512Mb density

- 24-ball FBGA package

- Automotive, AEC-Q100 grade 2 (-40°C to +105°C) temperature range

Technical Attributes

Find Similar Parts

| Description | Value | |

|---|---|---|

| 200 MHz | ||

| HyperRAM | ||

| FBGA | ||

| Surface Mount | ||

| 64M x 8bit | ||

| 512 Mbit | ||

| 24 | ||

| 105 °C | ||

| -40 °C | ||

| 1.8 V V |

ECCN / UNSPSC / COO

| Description | Value |

|---|---|

| Country of Origin: | RECOVERY FEE |

| ECCN: | 3A991B2 |

| HTSN: | 8542320041 |

| Schedule B: | 8542320040 |