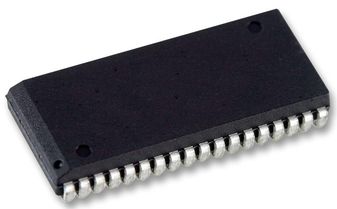

AS7C34096A-12JCN

SRAM Chip Async Single 3.3V 4M-Bit 512K x 8 12ns 36-Pin SOJ

- RoHS 10 Compliant

- Tariff Charges

AS7C34096A-12JCN is a high-performance CMOS 4,194,304-bit static random access memory (SRAM) device organized as 524,288 words × 8bits. It is designed for memory applications where fast data access, low power, and simple interfacing are desired. Equal address access and cycle times (tAA, tRC, tWC) of 10/12/15/20 ns with output enable access times (tOE) of 4/5/6/7 ns are ideal for high-performance applications. The chip enable input CE permits easy memory expansion with multiple-bank memory systems. When active-low CE is high the device enters standby mode. The device is guaranteed not to exceed 28.8mW power consumption in CMOS standby mode. All chip inputs and outputs are TTL-compatible, and operation is from a single 3.3V supply voltage.

- Organization: 524,288 words × 8bits, centre power and ground pins

- High speed, equal access and cycle times

- Low power consumption, 650mW/max at 10ns active, 28.8mW/max CMOS standby

- Easy memory expansion with active-low CE, active-low OE inputs

- TTL-compatible, three-state I/O

- ESD protection = 2000volts

- Latch-up current = 200mA

- Access time is 12ns

- SOJ 400 mil package

- Commercial temperature range from 0°C to 70°C

Technical Attributes

Find Similar Parts

| Description | Value | |

|---|---|---|

| 19 Bit | ||

| 4 Mbit | ||

| SOJ | ||

| Surface Mount | ||

| 150 mA | ||

| 12 ns | ||

| 512K x 8bit | ||

| 4 Mbit | ||

| Surface Mount | ||

| 36 | ||

| 8 Bit | ||

| 8 Bit | ||

| 1 | ||

| 512 kWords | ||

| 0 to 70 °C | ||

| 70 °C | ||

| 0 °C | ||

| 36SOJ | ||

| 36 | ||

| 23.62 x 10.16 x 2.95 mm | ||

| No | ||

| Commercial | ||

| Asynchronous SRAM | ||

| SOJ | ||

| 3.6 V | ||

| 3 V | ||

| 3.3 V | ||

| Asynchronous | ||

| 3.3000 V |

ECCN / UNSPSC / COO

| Description | Value |

|---|---|

| Country of Origin: | RECOVERY FEE |

| ECCN: | EAR99 |

| HTSN: | 8542320041 |

| Schedule B: | 8542320040 |