Step0:Vitis HLSとVivadoのインストール

まだインストールしていない場合はhttps://japan.xilinx.com/support/download/index.html/content/xilinx/ja/downloadNav/vitis.htmlからVitisのインストールをお願いします。Vitisをインストールする際にVitis HLSとVivadoも自動的にインストールされます。次回はVivadoをメインとする内容にする予定です。

Step1: ソースコードの実装

初めにVitis HLSを立ち上げ、Create Projectをクリックして新しいプロジェクトを作成します

Project Nameを入れてNextをクリックします(ここではfibonacci_sequenceとしました)

何も指定せずNext → Nextとします

使用するボード・パーツ(ここではKR260)を選択してFinishをクリックします

Source → New Source Fileからソースファイルの作成を行います

ファイル名をadd.cppとして作成します

下に示すソースコードをコピー&ペーストします

// 変数のアドレスから値を取得して足し算する関数

void add(int *a, int *b, int *result) {

*result = *a + *b;

}

上記のソースコードは変数aのアドレス、変数bのアドレス、変数resultのアドレスを引数に取って、resultの値をaとbの値の和に書き換えています 変数やアドレスの詳細な説明はここでは割愛します 直感的に説明すると、aとbが記憶している数の和をresultに記憶させているという感じです

Step2: テストベンチの作成とシミュレーション

今回のテストベンチでは、フィボナッチ数列を出力するプログラムを作成します フィボナッチ数列の第n項は次のように定義されます(nは正の整数)

即ち、フィボナッチ数列は初項と第2項が1、第3項以降が前2つの項の和になっている数列です

具体的には、1, 1, 2, 3, 5, 8, ... のような数列になります

初項を0で定義する場合もありますが、本質的なところは変わりません

Test Bench → New Test Bench Fileからテストベンチファイルの作成を行います

ファイル名をmain.cppとして作成します 下に示すソースコードをコピー&ペーストします

#include <iostream> // 入出力用ライブラリの呼び出し

void add(int *a, int *b, int *result); // 足し算用関数の宣言

// ここからテストベンチ

int main()

{

int n = 10; // フィボナッチ数列の項数

int i; // ループ用変数 (i = 1, 2, ...,n)

int a = 1, b = 1; // フィボナッチ数列の第i項と第i+1項

int ans_sw, ans_hw; // ソフトウェアでの足し算の結果とハードウェアでの足し算の結果

int fail_num = 0; // 結果が正しいかどうか判定するフラグ変数

// 第n項までのフィボナッチ数列の計算

for (i = 1; i <= n; i++) {

ans_sw = a + b; // 第i項と第i+1項の和(ソフトウェア処理)

add(&a, &b, &ans_hw); // 第i項と第i+1項の和(ハードウェア処理)

// ハードとソフトで結果が合わなければフラグ変数を1増やす

if (ans_hw != ans_sw) {

fail_num += 1;

}

std::cout << a << ", "; // フィボナッチ数列の第i項を出力

a = b; // 第i項を第i+1項に置き換える

b = ans_sw; // 第i+1項を第i+2項に置き換える

}

// ハードとソフトの結果が完全に一致していれば成功、そうでなければ失敗

if (fail_num == 0) {

std::cout << " SUCCESS!" << std::endl;

return 0;

}else{

std::cout << " FAIL..." << std::endl;

return -1;

}

}

作成したソースコードとテストベンチを用いて、シミュレーションを行います

前段階として、高位合成する関数を設定します

ProjectタブのProject Settingsを選択します

Synthesisを選択し、そのTop Functionにaddを設定してOKをクリックします

Run Flow アイコンをクリックしてC Simulationを選択します

そのままOKをクリックするとシミュレーションが開始されます

下の図の様にフィボナッチ数列の第10項までとSUCCESS!が表示されれば成功です

Step3: 足し算IPの作成

高位合成(高級プログラミング言語からハードウェア記述言語への変換)を実行します

Run Flow アイコンからC Synthesisを選択します

高位合成が終わって下の図のようになれば成功です

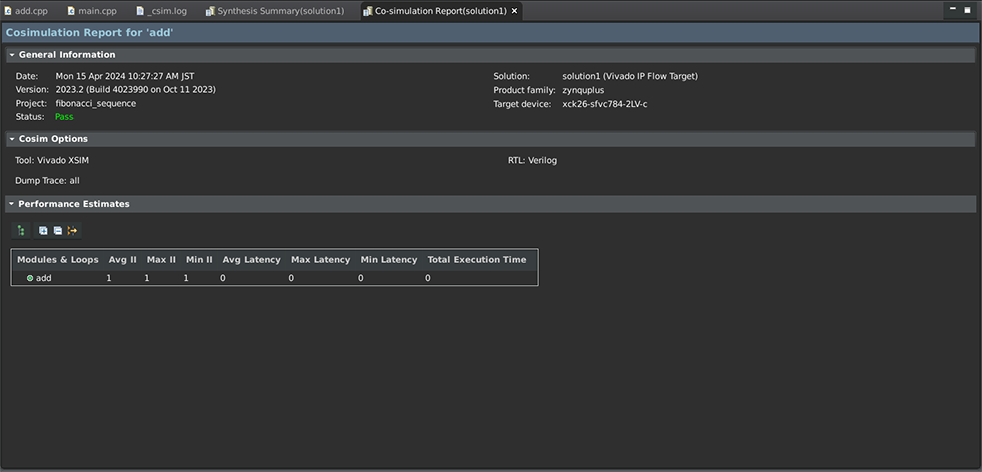

出力されたハードウェア記述言語の動作検証を、C/RTL協調シミュレーションで行います

Run Flow アイコンからCosimulationを選択します

Dump Traceをallにしておくと、RTLシミュレーションの波形が確認できます

C/RTL協調シミュレーションが終わって下の図のようになれば成功です

Open Wave ViewerアイコンをクリックするとVivadoが開くのでRTLシミュレーションの波形を確認します。

最後にハードウェアIPの作成を行います

Run Flow アイコンからExport RTLを選択します

そのままOKをクリックすれば、IPが作成されます

感想

今回はVitis HLSでのプログラミングとIPの作成を行いました。プログラミングに慣れている人なら難易度はそれほど高くなかったと思います。私のようなソフト屋からするとこういったツールはとても頼もしく思えます。将来的にVitis HLSはVitis Unified IDEに置き換わるようなので、今後はそちらを使った記事も書くかもしれません。 今回のページ作成にはhttps://phys-higashi.com/826/を大きく参考にさせていただきました。 それでは、また次回お会いしましょう!See you next time!

Kria

Kria SOMはアダプティブSoCデバイスを搭載しており、スマートカメラやエンベデッドビジョンなどに最適です。

AMD製品に関連する技術ブログ

- エンジニアブログの再開およびテクニカルウェビナーのご案内

- 初心者のためのPython & Numpy入門

- KR260でIntel RealSenseを動かしてみた!

- Vitis HLSで足し算IPを作ってみた!(プログラミング編)

- KD240でモータ制御してみた!

- KR260でデジタル信号処理してみた! (3)

- KR260でデジタル信号処理してみた! (2)

- KR260でデジタル信号処理してみた! (1)

- KR260でロボットアームを動かしてみた! (2)

- KR260でロボットアームを動かしてみた! (1)

- KR260でROS2を使ってキャリブレーション&マーカー検出してみた!

- KR260とPynqでAIカメラを動かしてみた!

- KR260でROS2 Perception Stack Applicationを動かしてみた!【2】

- KR260でROS2 Perception Stack Applicationを動かしてみた!

- Kria SOMでTPM2.0を動かしてみた!

- VivadoでKR260のハードウェアデザインを作って動かしてみた!

- ROS2 Multi-Node Communications via TSNを動かしてみた!

- AIBOX-ReIDを動かしてみた!