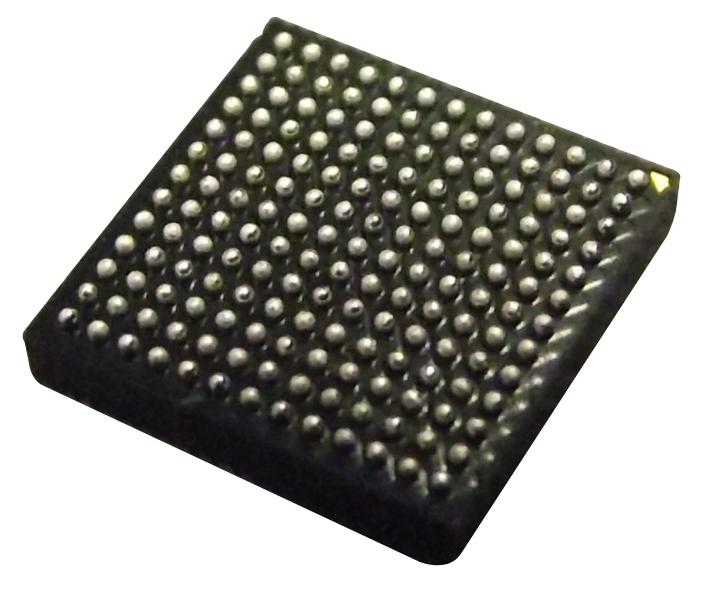

MT40A512M16TB-062E:R

DRAM, DDR4, 8 Gbit, 512M x 16bit, 1.6 GHz, FBGA, 96 Pins

MT40A512M16TB-062E:R is a DDR4 SDRAM. It is a high-speed dynamic random-access memory internally configured as an eight-bank DRAM for the x16 configuration and as a 16-bank DRAM for the x4 and x8 configurations. The DDR4 SDRAM uses an 8n-prefetch architecture to achieve high-speed operation. The 8n-prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single READ or WRITE operation for the DDR4 SDRAM consists of a single 8n-bit wide, four-clock data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

- 512 Meg x 16 configuration, tCK = 0.625ns, CL = 21 (cycle time)

- 8n-bit prefetch architecture, programmable data strobe preambles

- Data strobe preamble training, command/Address latency

- Multipurpose register READ and WRITE capability, write lev

- Self refresh mode, low-power auto self refresh, temperature controlled refresh

- Fine granularity refresh, self refresh abort, maximum power

- Output driver calibration, data bus inversion (DBI) for data

- Command/Address (CA) parity, data bus write cyclic redundancy check

- Per-DRAM addressability, connectivity test, JEDEC JESD-79-4 comp

- Industrial temperature range from -40°C to 95°C, 96-ball FBGA package

Technical Attributes

Find Similar Parts

| Description | Value | |

|---|---|---|

| 1.6 GHz | ||

| DDR4 | ||

| FBGA | ||

| Surface Mount | ||

| 512M x 16bit | ||

| 8 Gbit | ||

| 96 | ||

| 95 °C | ||

| 0 °C | ||

| 1.2 V |

ECCN / UNSPSC / COO

| Description | Value |

|---|---|

| Country of Origin: | null |

| ECCN: | EAR99 |

| HTSN: | null |

| Schedule B: | null |