MT48LC2M32B2B5-6A IT:J

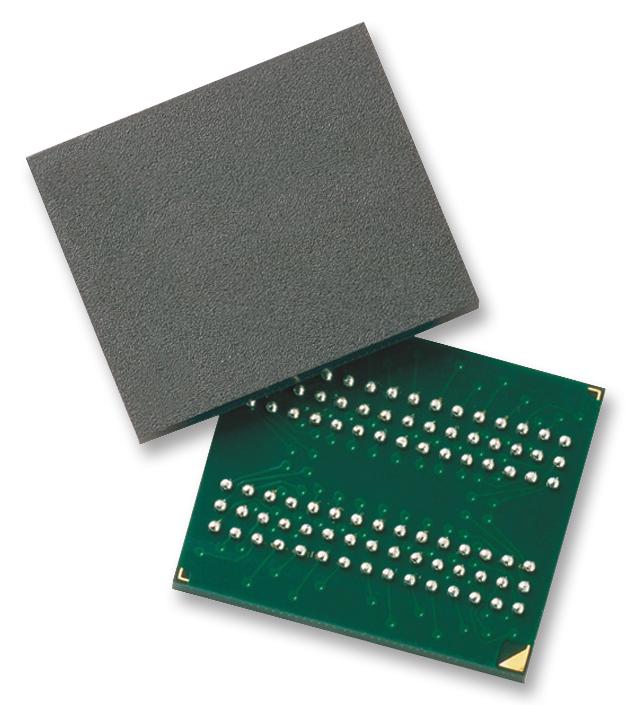

DRAM, SDR, 64 Mbit, 2M x 32bit, 167 MHz, VFBGA, 90 Pins

MT48LC2M32B2B5-6A IT:J is a SDR SDRAM. It uses a 64Mb SDRAM and a high-speed CMOS, dynamic random-access memory containing 67,108,864 bits. It is internally configured as a quad-bank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the x4’s 67,108,864-bit banks are organized as 8192 rows by 2048 columns by 4 bits. Each of the 16,777,216-bit banks are organized as 2048 rows by 256 columns by 32bits. It supports CAS latency (CL) of 1, 2, and 3.

- Operating supply voltage range is 3V to 3.6V (VDD, VDDQ)

- 2Meg x 32 configuration (512K x 32 x 4 banks), PC100-compliant

- Packaging style is 90-ball VFBGA (8mm x 13mm)

- Clock frequency is 167MHz, auto refresh

- Industrial temperature range is –40°C to +85°C

- Fully synchronous to all signals registered on positive edge of system clock

- Internal pipelined operation; column address can be changed every clock cycle

- Internal banks for hiding row access/precharge

- Auto precharge, includes concurrent auto precharge and auto refresh modes

- LVTTL-compatible inputs and outputs

Technical Attributes

Find Similar Parts

| Description | Value | |

|---|---|---|

| 13 Bit | ||

| 167 MHz | ||

| 32 Bit | ||

| 64 Mbit | ||

| SDRAM | ||

| VFBGA | ||

| Surface Mount | ||

| 167 MHz | ||

| 120 mA | ||

| 5.4 ns | ||

| 2M x 32bit | ||

| 64 Mbit | ||

| Surface Mount | ||

| 90 | ||

| 32 Bit | ||

| 32 Bit | ||

| 80 V | ||

| -40 to 85 °C | ||

| 85 °C | ||

| -40 °C | ||

| 90VF-BGA | ||

| 90 | ||

| 13 x 8 x 0.65 mm | ||

| Industrial | ||

| VFBGA | ||

| 3.3 V | ||

| SDRAM |

ECCN / UNSPSC / COO

| Description | Value |

|---|---|

| Country of Origin: | null |

| ECCN: | EAR99 |

| HTSN: | 8542320032 |

| Schedule B: | 8542320015 |