Leading system developers are using All Programmable Devices in next generation vision guided machine learning systems. To accelerate productivity, Xilinx has created the reVISION Zone to aggregate useful resources for software, hardware and system developers.

For developers who wish to share their reference designs, libraries, and experience, we have also included a section with community projects.

Begin today by exploring this zone and get started building responsive and reconfigurable vision guided systems.

Differentiating Advantages

- More Responsive than typical SoCs & Embedded GPUs

- Reconfigurable to the Latest Algorithms and Sensors

- Software Defined &Improved Ease of Use

| More Responsive than Typical SoCs & Embedded GPUs: | Reconfigurable to the Latest Algorithms and Sensors: | Software Defined & Improved Ease of Use: |

|---|---|---|

|

|

|

Computer Vision

Being able to implement computer vision algorithms in Zynq SoCs/MPSoCs and FPGAs enables developers to create highly responsive and reconfigurable vision guided systems. These systems are capable of performing at up to 42x frames/sec/Watt better than alternative GPU-based SoCs. Traditionally implementing computer vision algorithms in Zynq and FPGA devices has required a very tight collaboration among software and hardware teams that have limited the ability for software developers to leverage the high performance capability of the technology platform. SDSoC along with the OpenCV library is now opening up the Zynq platform to a whole new group of users. Xilinx will also introduce framework support for OpenVX graph-based design in second half 2017.

OpenCV library functions are essential to developing many computer vision applications. Xilinx’s library for computer vision, based on key OpenCV functions, will allow you to easily compose and accelerate computer vision functions in the FPGA fabric through SDx or HLx environments. In addition, Xilinx library functions are consistent with OpenCV and are optimized for performance, resource utilization and ease of use.

- Thousands of functions in the OpenCV 3.1 library are available to run on the ARM Cortex™-A9 and Cortex A53 cores in Zynq

- ~45 OpenCV functions (the OpenVX subset) are available as a library of RTL optimized functions for Xilinx SoCs

- Complete library user guide with device utilization and performance

- Support for 1 and 8 pixel parallel versions is available for most functions

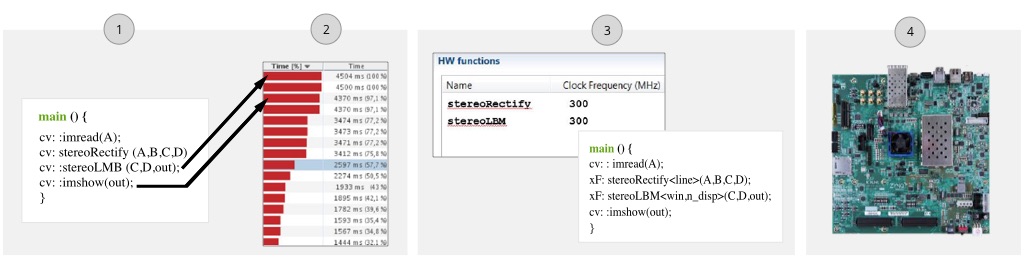

reVISION Design Flow for Computer Vision

- Cross-compile OpenCV application Zynq (ARM A9/A53

- Profile and identify bottleneck functions

- Minimal changes to the code and set functions to hardware. Compile using SDSoC

- Copy generated SW/HW images to SDCard and run on a Zynq board

Machine Learning

Machine learning and deep learning have gained attention from the development community as a technique that provides enhanced intelligence to many applications including Embedded Vision. While not a new discipline, relatively new breakthroughs in algorithms, access to large data sets for algorithm training and efficient and economically more viable computing platforms have resulted in very rapid interest and adoption of the technology.

Xilinx’s Zynq SoCs/MPSoCs are an ideal fit for machine learning, achieving 6X better images/sec/Watt in machine learning inference relative to embedded GPUs and typical SoCs. Xilinx’s reVISION Stack removes traditional design barriers by allowing you to quickly take a trained network and deploy it on Zynq SoCs and MPSoCs for inference.

Features:

- Full software stack for deploying machine learning applications

- Hardware optimized libraries supporting Conv, ReLU, Pooling, Dilated conv, Deconv, FC, Detector & Classifier, SoftMax layers

- Caffe inter-operability allows easy porting from Proto-Text files for Network definition and trained weights

- Optimized reference models available for a wide range of network topologies, such as AlexNet, GoogLeNet, SqueezeNet, FCN and SSD

- Networks can be customized through software running on the ARM processor without lengthy compilation