# **VE2302 SOM Hardware User Guide**

Version 1.2

## **Contents**

| D | ocum   | ent   | Control                                                                   | 8  |

|---|--------|-------|---------------------------------------------------------------------------|----|

| V | ersion | n His | story                                                                     | 8  |

| 1 | Intr   | odu   | ction                                                                     | 9  |

|   | 1.1    | Add   | litional Information                                                      | 11 |

| 2 | Fur    | nctic | onal Description                                                          | 12 |

|   | 2.1    |       | D Versal™ AI Edge                                                         |    |

|   | 2.2    |       | mory                                                                      |    |

|   | 2.2.   | 1     | LPDDR4                                                                    | 12 |

|   | 2.2.   | 2     | Octal SPI Flash                                                           | 16 |

|   | 2.2.   | 3     | eMMC Flash                                                                | 17 |

|   | 2.2.   | 4     | SFVA784 Device Package Delay Compensation for Memory Interfaces           | 18 |

|   | 2.3    | GT`   | YP Transceiver Interface                                                  | 19 |

|   | 2.3.   | 1     | SFVA784 Device Package Delay Compensation for GTYP Transceiver Interfaces | 21 |

|   | 2.4    | USI   | 3 2.0 PHY                                                                 | 21 |

|   | 2.4.   | 1     | SFVA784 Device Package Delay Compensation for USB2.0 Interfaces           | 22 |

|   | 2.5    | Eth   | ernet PHY                                                                 | 22 |

|   | 2.5.   | 1     | SFVA784 Device Package Delay Compensation for Ethernet Interface          | 24 |

|   | 2.6    | I2C   | 8-Bit I/O Expander                                                        | 24 |

|   | 2.6.   | .1    | Carrier Card I2C Expander GPIO Pins                                       | 26 |

|   | 2.7    | 2-C   | hannel I2C Switch                                                         | 26 |

|   | 2.7.   | 1     | Carrier Card I2C Interface                                                | 28 |

|   | 2.7.   | 2     | PMBUS Interface                                                           | 29 |

|   | 2.8    | I2C   | MAC EEPROM                                                                | 29 |

|   | 2.9    | Use   | er IO Pins                                                                | 30 |

|   | 2.9.   | 1     | Processor MIO User Pins                                                   |    |

|   | 2.9.   | 2     | Programmable Logic IO User Pins                                           | 31 |

|   | 2.9.   | 3     | SFVA784 Device Package Delay Compensation for User I/O Interfaces         | 31 |

|   | 2.10   | Clo   | ck Sources                                                                | 31 |

|   | 2.11   | Cor   | ntrol Signal Sources                                                      | 32 |

|   | 2.11   | 1.1   | Power-On Reset (POR) Control Signal                                       | 32 |

|   | 2.11   | 1.2   | Power Supply Sequencing Control Signals                                   | 33 |

|   | 2.11   | 1.3   | PUDC_B Control Signal and Status Signals                                  | 34 |

|   | 2.11   | 1.4   | On-Board Peripheral Reset Control                                         | 34 |

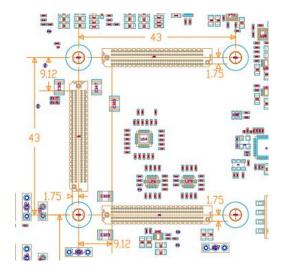

|   | 2.12   | Exp   | ansion Headers                                                            |    |

|   | 2.12   | 2.1   | Micro Headers                                                             | 35 |

|   | 2.12   | 2.2   | JX Micro Headers Matched Lengths                                          | 37 |

|   | 2.12 | 2.3    | JX Connector Master Table                                | 37  |

|---|------|--------|----------------------------------------------------------|-----|

|   | 2.13 | Sup    | ported Configuration Modes                               | 48  |

|   | 2.14 | JTA    | G Interface                                              | 49  |

|   | 2.15 | Pow    | ver Supplies                                             | 49  |

|   | 2.15 | 5.1    | Power Requirements                                       | 49  |

|   | 2.15 | 5.2    | Power Sequencing                                         | 51  |

|   | 2.15 | 5.3    | PCB Bypass / Decoupling Strategy                         | 54  |

|   | 2.15 | 5.4    | Power Estimation Using PDM                               | 54  |

|   | 2.15 | 5.5    | Speed Grades, Temperature Grades, and Operating Voltages | 54  |

|   | 2.15 | 5.6    | System Monitor (SYSMON) Interface                        | 55  |

|   | 2.15 | 5.7    | Battery Backup – Device Secure Boot Encryption Key       | 55  |

|   | 2.15 | 5.8    | Thermal Management                                       | 56  |

| 3 | Dev  | vice   | Bank Allocation                                          | 57  |

|   | 3.1  | PMC    | C and LPD MIO Bank Allocation                            | 57  |

|   | 3.2  | Dev    | ice Bank Voltages                                        | 57  |

| 4 | Spe  | ecific | cations and Ratings                                      | .58 |

|   | 4.1  | Abs    | olute Maximum Ratings                                    | 58  |

|   | 4.2  | Rec    | ommended Operating Conditions                            | 60  |

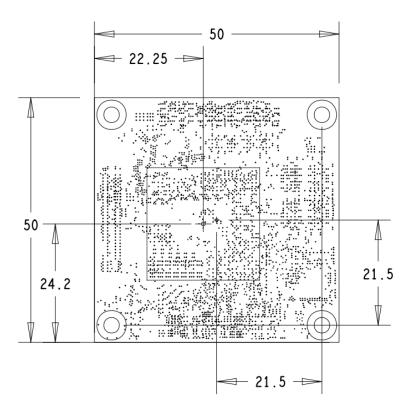

| 5 | Ме   | char   | nical Dimensions                                         | 63  |

| 6 | Ver  | sal⊺   | <sup>™</sup> AI Edge Development Kit                     | 64  |

| 7 | Get  | tting  | Help and Support                                         | 65  |

| 8 |      |        | Information                                              |     |

|   | 8.1  |        | claimer                                                  |     |

|   | 8.2  |        | nded Use                                                 |     |

|   | 8.3  |        | IS Compliance                                            |     |

|   | 8.4  |        | ctrostatic Discharge                                     |     |

|   | 8.5  |        | ranty                                                    | 67  |

# **Figures**

| Figure 1 – VE2302 SOM Block Diagram                     | 11 |

|---------------------------------------------------------|----|

| Figure 2 – LPDDR4 Block Diagram                         | 13 |

| Figure 3 – OSPI Circuit                                 | 17 |

| Figure 4 – eMMC Circuit                                 | 18 |

| Figure 5 – GTYP Quad 103 and 104 Connections            | 19 |

| Figure 6 – USB2.0 Circuit                               | 21 |

| Figure 7 – Ethernet PHY Circuit                         | 23 |

| Figure 8 – I2C I/O Expander Circuit                     | 25 |

| Figure 9 – I2C I/O Expander Addressing                  | 26 |

| Figure 10 – 2 Channel I2C Switch Circuit                | 27 |

| Figure 11 – I2C Switch Addressing                       | 28 |

| Figure 12 – I2C EEPROM Circuit                          | 29 |

| Figure 13 – EEPROM I2C Addressing                       | 30 |

| Figure 14 – SYSCLK Provided Termination                 | 32 |

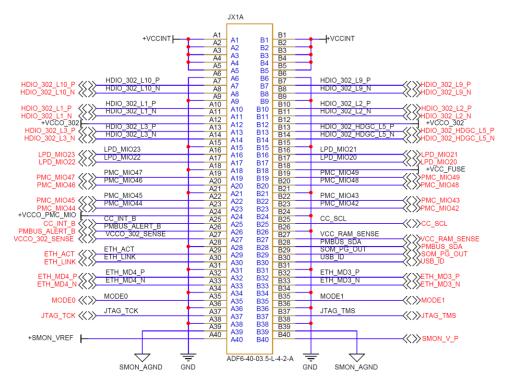

| Figure 15 – JX1 Row A/B Connector Pinout                | 45 |

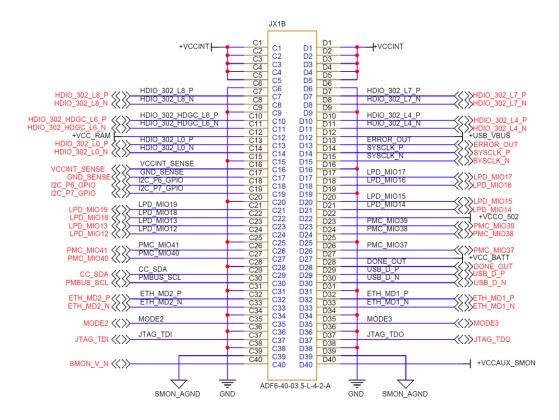

| Figure 16 – JX1 Row C/D Connector Pinout                | 46 |

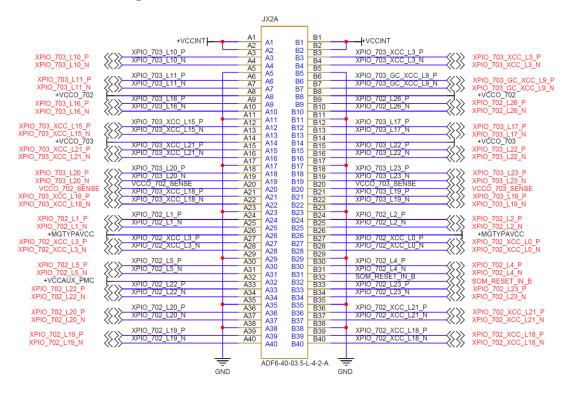

| Figure 17 – JX2 Row A/B Connector Pinout                | 46 |

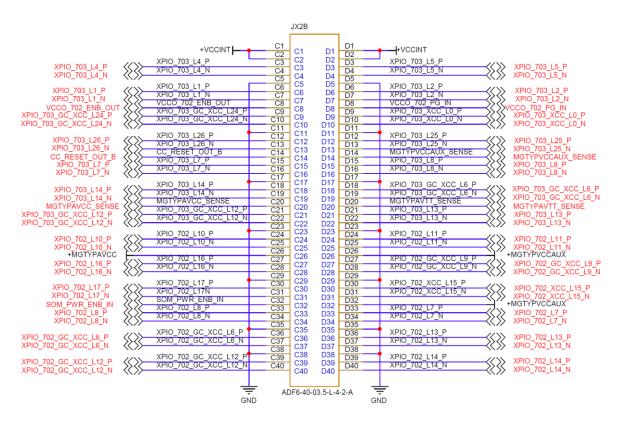

| Figure 18 – JX2 Row C/D Connector Pinout                | 47 |

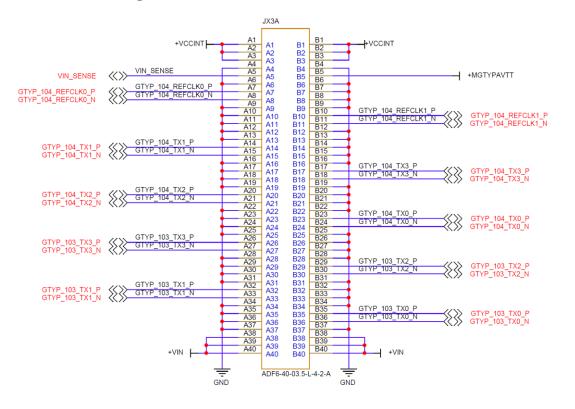

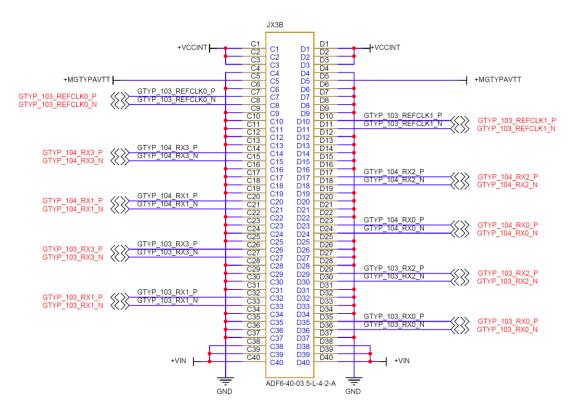

| Figure 19 – JX3 Row A/B Connector Pinout                | 47 |

| Figure 20 – JX3 Row C/D Connector Pinout                | 48 |

| Figure 21 – Versal Power-On Sequence                    | 52 |

| Figure 22 – Power Sequencing with End-User Carrier Card | 53 |

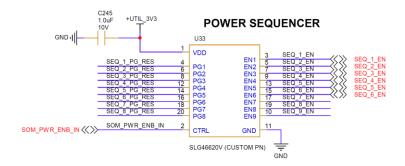

| Figure 23 – Custom Power Sequencer Circuit              | 53 |

| Figure 24 – Example Heat Sink and Fan Assembly (TBD)    | 56 |

| Figure 25 – Mechanical Dimensions – Top                 | 63 |

| Figure 26 – Mechanical Dimensions – Bottom              | 63 |

| Figure 27 – Mechanical Dimensions – Height (TBD)        | 64 |

| Figure 28 – Versal™ Al Edge Development Kit             | 64 |

## **Tables**

| Table 1 – Glossary10                                       |

|------------------------------------------------------------|

| Table 2 – LPDDR4 U23 Connections                           |

| Table 3 – LPDDR4 U24 Connections                           |

| Table 4 – Octal-SPI Flash Pin Assignment and Definitions   |

| Table 5 – eMMC Pin Assignment and Definitions              |

| Table 6 – Quad 103 and 104 GTYP Pin Assignments21          |

| Table 7 – USB2.0 PHY JX1 Pin Assignments                   |

| Table 8 – ULPI Pin Assignment and Definitions              |

| Table 9 – Ethernet PHY JX1 Pin Assignments23               |

| Table 10 – Ethernet RGMII Pin Assignments24                |

| Table 11 – I2C TRM Pin Mapping25                           |

| Table 12 – ONSemi FXL6408UMX Pin Mapping25                 |

| Table 13 – IO Expander Pin Functions and Definitions       |

| Table 14 – IO Expander GPIO PIN Assignments26              |

| Table 15 – I2C TRM Pin Mapping27                           |

| Table 16 – ONSemi PCA9543A Pin Mapping27                   |

| Table 17 – I2C Switch Channel Usage28                      |

| Table 18 – Carrier Card I2C Net Mapping29                  |

| Table 19 – PMBUS JX1 Connector Mapping29                   |

| Table 20 – I2C TRM Pin Mapping30                           |

| Table 21 – Microchip AT24MAC402 Pin Mapping30              |

| Table 22 – RTC Crystal Pin Assignments                     |

| Table 23 – LPDDR4 System Clock Pin Assignments             |

| Table 24 – Power-On Reset Control Pin Assignments          |

| Table 25 – Power Supply Sequencing Control Pin Assignments |

| Table 26 – Configuration Status Signal Pin Assignments     |

| Table 27 – Micro Header JX1 Summary36                      |

| Table 28 – Micro Header JX2 Summary36                      |

| Table 29 – Micro Header JX3 Summary                        |

| Table 30 – JX1 Connector Pin-out40                         |

| Table 31 – JX2 Connector Pin-out43                         |

| Table 32 – JX3 Connector Pin-out45                         |

| Table 33 – Supported BOOT Modes                         | 48 |

|---------------------------------------------------------|----|

| Table 34 – Boot Mode Interface Pin Assignments          | 49 |

| Table 35 –JTAG Interface Pin Assignments                | 49 |

| Table 36 – Example Power Requirements                   | 51 |

| Table 37 – Power Sequencing Control Signals             | 54 |

| Table 38 – SYSMON Connections                           | 55 |

| Table 39 – VCC_BATT Connection                          | 55 |

| Table 40 – Peripheral MIO Bank Interface Requirements   | 57 |

| Table 41 – GPIO MIO Bank Interface Requirements         | 57 |

| Table 42 – Bank Voltage Assignments                     | 58 |

| Table 43 – Absolute Maximum Temperature Rating          | 58 |

| Table 44 – Absolute Maximum Ratings for Supply Voltages | 59 |

| Table 45 – Absolute Maximum Ratings for I/O Voltages    | 60 |

| Table 46 – Recommended Supply Voltages                  | 61 |

| Table 47 – Recommended Ratings for I/O Voltages         | 62 |

## **Document Control**

**Document Version:** 1.2

**Document Date :** 5 August 2025

Document Author(s): Lorenzo Radaele

Donny Saveski

# **Version History**

| Version | Date      | Comment                    |

|---------|-----------|----------------------------|

| 1.0     | 6/6/2025  | Initial Release            |

| 1.1     | 6/30/2025 | Master JX Table Correction |

| 1.2     | 8/5/2025  | Master JX Table Correction |

#### 1 Introduction

The Tria Technologies VE2302 SOM (System-On-Module) is a high-performance product targeted for broad use in many applications. The goal of the module is to offer a compact SOM (50mm x 50mm) solution with an AMD Versal™ AI Edge device in commercial (0C to 70C) and industrial (-40C to 85C) temperature grades for engineers to adopt in development, proof-of concept, and production designs. The features provided by the VE2302 SOM consist of:

- AMD XCVE2302-1LSESFVA784 (Pin compatible with the XCVE2202 device)

- Pin compatible with the XCVE2102, XCVE2202, and XCVM1102

- Primary configuration options: OSPI flash

- o Auxiliary configuration options via end user carrier card:

- JTAG

- microSD card

- Memory

- LPDDR4 SDRAM (4GB, 2x32)

- o PMC OSPI Flash (Octal 256MB)

- o PMC eMMC Flash (x8 32GB)

- o I2C MAC EEPROM (2Kb)

- Interfaces

- PMC USB 2.0 ULPI PHY (Connector required on end user carrier card)

- Gigabit Ethernet RGMII PHY (Connector required on end user carrier card)

- o I2C 8-bit I/O Expander

- 2-channel I2C Switch/Mux

- o 3 JX Micro-Header Connectors (3 x 160-pin)

- 80 User XPIO Pins

- 22 User HDIO Pins

- 12 User LPD MIO Pins

- 13 User PMC MIO Pins

- 8 GTYP Transceivers

- 4 GTYP Reference Clock Inputs

- PMC JTAG Interface

- PMC SYSMON interface

- USB 2.0 Connector Interface

- Gigabit Ethernet RJ45 Connector Interface

- PMBus Interface

- Carrier Card I2C Interface

- SOM +VCC\_BATT Battery Input

- SOM Reset Input

- Carrier Card Interrupt Input

- Carrier Card Reset Output

- SOM Power Good Output

- SOM to Carrier Card Ground Pins

- SOM Input Voltages and Output Sense Pins

- o Reference Clock

- 33.333 MHz OSC

- Real Time Clock (RTC)

- Power

- On-Board Voltage Regulators

- o Custom Power Sequencer (Supports power-up and power-down sequencing)

- Bank I/O and GTYP Transceiver Voltage Rails (Supplied via end user carrier card)

- Pertinent URLs

- VE2302 SOM: http://avnet.me/ve2302-som

- o VE2302 Development Kit: http://avnet.me/ve2302-dk

The following table is a glossary of acronyms that will be used in description of the VE2302 SOM, and the peripherals attached to the Adaptive SoC Processing Sub-System and Programmable Logic Sub-System.

| Term   | Definition                      |

|--------|---------------------------------|

| PS     | Adaptive SoC Processing System  |

| PL     | Adaptive SoC Programmable Logic |

| MIO    | Multiplexed Input Output Pins   |

| LPD    | Low Power Domain                |

| PMC    | Platform Manager Controller     |

| PLM    | Platform Loader and Manager     |

| POR    | Power On Reset                  |

| APU    | Application Processing Unit     |

| RPU    | Real-time Processing Unit       |

| GPU    | Graphics Processing Unit        |

| SYSMON | System Monitor                  |

| ADC    | Analog-to-Digital Converter     |

| HDIO   | High Density PL I/O Pins        |

| XPIO   | High Performance PL I/O Pins    |

| PMBus  | Power Management Bus            |

| PDM    | Power Design Manager            |

Table 1 - Glossary

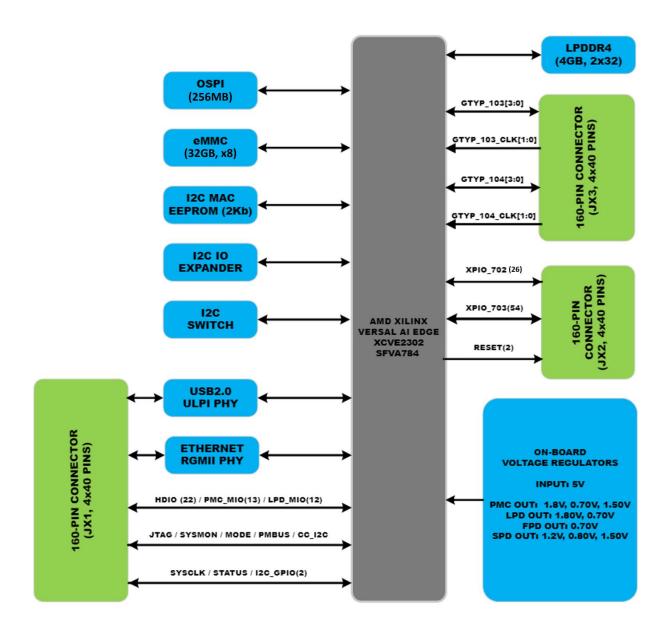

The following figure is a high-level block diagram of the VE2302 SOM and the peripherals attached to the Adaptive SoC Processing Sub-System and Programmable Logic Sub-System.

Figure 1 - VE2302 SOM Block Diagram

#### 1.1 Additional Information

Additional information and documentation on the AMD Versal™ Adaptive SoC can be found Here: https://www.amd.com/en/products/adaptive-socs-and-fpgas/versal.html

### **2 Functional Description**

#### 2.1 AMD Versal™ Al Edge

The VE2302 SOM provides the flexibility and versatility for developers to enable designs with the AMD Versal™ AI Edge series. This System-On-Module (SOM) is a small form factor and full-featured board based on the AMD Versal™ AI Edge VE2302 device featuring 328K programmable logic cells with a Dualcore Arm® Cortex®-A72 Application Processing Units and Dual-core Arm Cortex-R5F Real Time Processing Units, as well as L1 and L2 cache and 256KB on-chip memory with ECC. The SOM provides a host of features to simplify application development with a custom carrier card.

The VE2302 SOM is offered in commercial temperature grade and industrial temperature grade options. The VE2302 SOM is populated by default with a **XCVE2302-1LSESFVA784** device. Optionally, the VE2302 SOM is footprint compatible with several other AMD devices including the XCVE2102, XCVE2202, and XCVM1102.

#### 2.2 Memory

The VE2302 SOM contains a hardened DDR memory controller that is utilized for LPDDR4-4200. The VE2302 SOM takes advantage of hardened DDR memory controller to provide system RAM as well as two different non-volatile memory sources.

#### 2.2.1 LPDDR4

The VE2302 SOM provides 4GB of LPDDR4 memory in a 2x32 configuration using two Micron MT53E512M32D1ZW-046 IT:B (200-pin BGA package) x32 devices. The LPDDR4 devices are implemented in 512Mb x 32 configuration and supports up to 3733 Mbps in a -1 VE2302 device using an operating voltage of 0.80V.

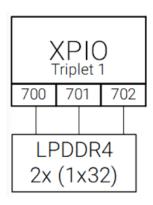

The LPDDR4 devices are connected to an XPIO triplet in banks 700, 701, and 702 and are operated at +1.1V at the maximum supported bandwidth available in the **PIN EFFICIENT** implementation on the AMD Versal™ AI Edge device. The **PIN EFFICIENT** implementation results in all but four (4) signals being implemented in banks 700 and 701.

A couple of issues arise when implementing the LPDDR4 interface in this manner. First issue is that four (4) signals with a bank voltage of +1.1V exist on bank 702 which creates a potential for a mismatch with the bank voltage if you desire to utilize bank 702 for a voltage other than the memory bank voltage, such as a bank voltage like 1.2V or 1.5V. A workaround for this exists and is documented in **AMD Answer Record 35358** which helps to resolve voltage standard conflicts for pin efficient topologies.

NOTE: Link to Answer Record 35358: <u>Versal™ Adaptive SOC DDRMC - Change LPDDR4 RESET N</u> and SYS\_CLK IO Standards for Pin Efficient Topologies

The second issue that arises when implementing the LPDDR4 interface with a **PIN EFFICIENT** implementation is that some of the XPIO pins in bank 702 are dedicated to the DDRMC (DDR Memory Controller) and cannot be utilized by end-users. This results in a total of 24 pins that cannot be utilized on Bank 702 because of the **PIN EFFICIENT** implementation. The pins that are DDRMC will be identified on the JX connector pinout. Please refer to the **Expansion Headers** section of this document for the DDRMC Bank 702 pins that should not be utilized.

The implementation of LPDDR4 interface on the VE2302 SOM ensures board trace lengths are matched, compensating for the internal package flight times of the XCVE2302 SoC SFVA784 package, to meet the requirements listed in the Versal™ Adaptive SoC PCB Design User Guide (<u>UG863</u>).

Figure 2 – LPDDR4 Block Diagram

| Signal Name         | Description                         | Bank 700<br>SoC Pin | LPDDR4<br>Pin U23 |

|---------------------|-------------------------------------|---------------------|-------------------|

| LPDDR4_CH0_DQ_A0    | LPDDR4 Data Byte 0                  | AB21                | B2                |

| LPDDR4_CH0_DQ_A1    | LPDDR4 Data Byte 0                  | AC20                | C2                |

| LPDDR4_CH0_DQ_A2    | LPDDR4 Data Byte 0                  | AB15                | E2                |

| LPDDR4_CH0_DQ_A3    | LPDDR4 Data Byte 0                  | AC16                | F2                |

| LPDDR4_CH0_DQ_A4    | LPDDR4 Data Byte 0                  | AC13                | F4                |

| LPDDR4_CH0_DQ_A5    | LPDDR4 Data Byte 0                  | AB14                | E4                |

| LPDDR4_CH0_DQ_A6    | LPDDR4 Data Byte 0                  | AB20                | C4                |

| LPDDR4_CH0_DQ_A7    | LPDDR4 Data Byte 0                  | AC22                | B4                |

| LPDDR4_CH0_DQ_A8    | LPDDR4 Data Byte 1                  | AE22                | B11               |

| LPDDR4_CH0_DQ_A9    | LPDDR4 Data Byte 1                  | AD22                | C11               |

| LPDDR4_CH0_DQ_A10   | LPDDR4 Data Byte 1                  | AD21                | E11               |

| LPDDR4_CH0_DQ_A11   | LPDDR4 Data Byte 1                  | AC14                | F11               |

| LPDDR4_CH0_DQ_A12   | LPDDR4 Data Byte 1                  | AD14                | F9                |

| LPDDR4_CH0_DQ_A13   | LPDDR4 Data Byte 1                  | AD17                | E9                |

| LPDDR4_CH0_DQ_A14   | LPDDR4 Data Byte 1                  | AC17                | C9                |

| LPDDR4_CH0_DQ_A15   | LPDDR4 Data Byte 1                  | AD20                | В9                |

| LPDDR4_CH0_DQS_T_A0 | LPDDR4 Data Byte 0 Data Strobe Pair | AB18                | D3                |

| LPDDR4_CH0_DQS_C_A0 | LPDDR4 Data Byte 0 Data Strobe Pair | AB17                | E3                |

| LPDDR4_CH0_DQS_T_A1 | LPDDR4 Data Byte 1 Data Strobe Pair | AD12                | D10               |

| LPDDR4_CH0_DQS_C_A1 | LPDDR4 Data Byte 1 Data Strobe Pair | AD11                | E10               |

| LPDDR4_CH0_DMI_A0   | LPDDR4 Data Byte 0 Data Mask        | AB12                | C3                |

| LPDDR4_CH0_DMI_A1   | LPDDR4 Data Byte 1 Data Mask        | AC19                | C10               |

| LPDDR4_CH0_DQ_B0    | LPDDR4 Data Byte 2                  | AF13                | AA2               |

| LPDDR4_CH0_DQ_B1    | LPDDR4 Data Byte 2                  | AG15                | Y2                |

| LPDDR4_CH0_DQ_B2    | LPDDR4 Data Byte 2                  | AF18                | V2                |

| LPDDR4_CH0_DQ_B3    | LPDDR4 Data Byte 2                  | AG18 | U2       |

|---------------------|-------------------------------------|------|----------|

| LPDDR4_CH0_DQ_B4    | LPDDR4 Data Byte 2                  | AF19 | U4       |

| LPDDR4_CH0_DQ_B5    | LPDDR4 Data Byte 2                  | AE19 | V4       |

| LPDDR4_CH0_DQ_B6    | LPDDR4 Data Byte 2                  | AF14 | Y4       |

| LPDDR4_CH0_DQ_B7    | LPDDR4 Data Byte 2                  | AG13 | AA4      |

| LPDDR4_CH0_DQ_B8    | LPDDR4 Data Byte 3                  | AH22 | AA11     |

| LPDDR4_CH0_DQ_B9    | LPDDR4 Data Byte 3                  | AG22 | Y11      |

| LPDDR4_CH0_DQ_B10   | LPDDR4 Data Byte 3                  | AG21 | V11      |

| LPDDR4_CH0_DQ_B11   | LPDDR4 Data Byte 3                  | AH20 | U11      |

| LPDDR4_CH0_DQ_B12   | LPDDR4 Data Byte 3                  | AH18 | U9       |

| LPDDR4_CH0_DQ_B13   | LPDDR4 Data Byte 3                  | AH17 | V9       |

| LPDDR4_CH0_DQ_B14   | LPDDR4 Data Byte 3                  | AH14 | Y9       |

| LPDDR4_CH0_DQ_B15   | LPDDR4 Data Byte 3                  | AH15 | AA9      |

| LPDDR4_CH0_DQS_T_B0 | LPDDR4 Data Byte 2 Data Strobe Pair | AG17 | W3       |

| LPDDR4_CH0_DQS_C_B0 | LPDDR4 Data Byte 2 Data Strobe Pair | AG16 | V3       |

| LPDDR4_CH0_DQS_T_B1 | LPDDR4 Data Byte 3 Data Strobe Pair | AG20 | W10      |

| LPDDR4_CH0_DQS_C_B1 | LPDDR4 Data Byte 3 Data Strobe Pair | AH19 | V10      |

| LPDDR4_CH0_DMI_B0   | LPDDR4 Data Byte 2 Data Mask        | AG12 | Y3       |

| LPDDR4_CH0_DMI_B1   | LPDDR4 Data Byte 3 Data Mask        | AH13 | Y10      |

| LPDDR4_CH0_CA_A0    | LPDDR4 Address Input                | AH12 | H2, R2   |

| LPDDR4_CH0_CA_A1    | LPDDR4 Address Input                | AE17 | J2, P2   |

| LPDDR4_CH0_CA_A2    | LPDDR4 Address Input                | AE14 | H9, R9   |

| LPDDR4_CH0_CA_A3    | LPDDR4 Address Input                | AD19 | H10, R10 |

| LPDDR4_CH0_CA_A4    | LPDDR4 Address Input                | AC11 | H11, R11 |

| LPDDR4_CH0_CA_A5    | LPDDR4 Address Input                | AE13 | J11, P11 |

| LPDDR4_CH0_CK_T_A0  | LPDDR4 Clock Device 0 Pair          | AD16 | J8, P8   |

| LPDDR4_CH0_CK_C_A0  | LPDDR4 Clock Device 0 Pair          | AD15 | J9, P9   |

| LPDDR4_CH0_CKE_A0   | LPDDR4 Clock Enable Input           | AE18 | J4, P4   |

| LPDDR4_CH0_CS_A0    | LPDDR4 Chip Select Input            | AG11 | H4, R4   |

|                     |                                     |      |          |

Table 2 - LPDDR4 U23 Connections

| Signal Name      | Description        | Bank 701<br>SoC Pin | DDR4 Pin<br>U24 |

|------------------|--------------------|---------------------|-----------------|

| LPDDR4_CH1_DQ_A0 | LPDDR4 Data Byte 0 | AA22                | B2              |

| LPDDR4_CH1_DQ_A1 | LPDDR4 Data Byte 0 | V23                 | C2              |

| LPDDR4_CH1_DQ_A2 | LPDDR4 Data Byte 0 | V24                 | E2              |

| LPDDR4_CH1_DQ_A3 | LPDDR4 Data Byte 0 | Y23                 | F2              |

| LPDDR4_CH1_DQ_A4    | LPDDR4 Data Byte 0                  | W25  | F4   |

|---------------------|-------------------------------------|------|------|

| LPDDR4_CH1_DQ_A5    | LPDDR4 Data Byte 0                  | W24  | E4   |

| LPDDR4_CH1_DQ_A6    | LPDDR4 Data Byte 0                  | Y22  | C4   |

| LPDDR4_CH1_DQ_A7    | LPDDR4 Data Byte 0                  | AA21 | B4   |

| LPDDR4_CH1_DQ_A8    | LPDDR4 Data Byte 1                  | AE24 | B11  |

| LPDDR4_CH1_DQ_A9    | LPDDR4 Data Byte 1                  | AG23 | C11  |

| LPDDR4_CH1_DQ_A10   | LPDDR4 Data Byte 1                  | AH25 | E11  |

| LPDDR4_CH1_DQ_A11   | LPDDR4 Data Byte 1                  | AH23 | F11  |

| LPDDR4_CH1_DQ_A12   | LPDDR4 Data Byte 1                  | AH24 | F9   |

| LPDDR4_CH1_DQ_A13   | LPDDR4 Data Byte 1                  | AG25 | E9   |

| LPDDR4_CH1_DQ_A14   | LPDDR4 Data Byte 1                  | AF25 | C9   |

| LPDDR4_CH1_DQ_A15   | LPDDR4 Data Byte 1                  | AD25 | B9   |

| LPDDR4_CH1_DQS_T_A0 | LPDDR4 Data Byte 0 Data Strobe Pair | Y24  | D3   |

| LPDDR4_CH1_DQS_C_A0 | LPDDR4 Data Byte 0 Data Strobe Pair | AA23 | E3   |

| LPDDR4_CH1_DQS_T_A1 | LPDDR4 Data Byte 1 Data Strobe Pair | AF24 | D10  |

| LPDDR4_CH1_DQS_C_A1 | LPDDR4 Data Byte 1 Data Strobe Pair | AF23 | E10  |

| LPDDR4_CH1_DMI_A0   | LPDDR4 Data Byte 0 Data Mask        | V22  | C3   |

| LPDDR4_CH1_DMI_A1   | LPDDR4 Data Byte 1 Data Mask        | AD24 | C10  |

| LPDDR4_CH1_DQ_B0    | LPDDR4 Data Byte 2                  | AG27 | AA2  |

| LPDDR4_CH1_DQ_B1    | LPDDR4 Data Byte 2                  | AG28 | Y2   |

| LPDDR4_CH1_DQ_B2    | LPDDR4 Data Byte 2                  | AE27 | V2   |

| LPDDR4_CH1_DQ_B3    | LPDDR4 Data Byte 2                  | AD26 | U2   |

| LPDDR4_CH1_DQ_B4    | LPDDR4 Data Byte 2                  | AE26 | U4   |

| LPDDR4_CH1_DQ_B5    | LPDDR4 Data Byte 2                  | AF26 | V4   |

| LPDDR4_CH1_DQ_B6    | LPDDR4 Data Byte 2                  | AH27 | Y4   |

| LPDDR4_CH1_DQ_B7    | LPDDR4 Data Byte 2                  | AG26 | AA4  |

| LPDDR4_CH1_DQ_B8    | LPDDR4 Data Byte 3                  | AB26 | AA11 |

| LPDDR4_CH1_DQ_B9    | LPDDR4 Data Byte 3                  | AB28 | Y11  |

| LPDDR4_CH1_DQ_B10   | LPDDR4 Data Byte 3                  | V25  | V11  |

| LPDDR4_CH1_DQ_B11   | LPDDR4 Data Byte 3                  | W27  | U11  |

| LPDDR4_CH1_DQ_B12   | LPDDR4 Data Byte 3                  | W26  | U9   |

| LPDDR4_CH1_DQ_B13   | LPDDR4 Data Byte 3                  | AA28 | V9   |

| LPDDR4_CH1_DQ_B14   | LPDDR4 Data Byte 3                  | Y26  | Y9   |

| LPDDR4_CH1_DQ_B15   | LPDDR4 Data Byte 3                  | AA26 | AA9  |

| LPDDR4_CH1_DQS_T_B0 | LPDDR4 Data Byte 2 Data Strobe Pair | AC28 | W3   |

| LPDDR4_CH1_DQS_C_B0 | LPDDR4 Data Byte 2 Data Strobe Pair | AD27 | V3   |

| LPDDR4_CH1_DQS_T_B1 | LPDDR4 Data Byte 3 Data Strobe Pair | V28  | W10  |

| ·                   |                                     |      |      |

| LPDDR4_CH1_DQS_C_B1 | LPDDR4 Data Byte 3 Data Strobe Pair | V27  | V10      |

|---------------------|-------------------------------------|------|----------|

| LPDDR4_CH1_DMI_B0   | LPDDR4 Data Byte 2 Data Mask        | AE28 | Y3       |

| LPDDR4_CH1_DMI_B1   | LPDDR4 Data Byte 3 Data Mask        | Y28  | Y10      |

| LPDDR4_CH1_CA_A0    | LPDDR4 Address Input                | AC27 | H2, R2   |

| LPDDR4_CH1_CA_A1    | LPDDR4 Address Input                | AF28 | J2, P2   |

| LPDDR4_CH1_CA_A2    | LPDDR4 Address Input                | AE23 | H9, R9   |

| LPDDR4_CH1_CA_A3    | LPDDR4 Address Input                | AC25 | H10, R10 |

| LPDDR4_CH1_CA_A4    | LPDDR4 Address Input                | W21  | H11, R11 |

| LPDDR4_CH1_CA_A5    | LPDDR4 Address Input                | AC24 | J11, P11 |

| LPDDR4_CH1_CK_T_A0  | LPDDR4 Clock Device 0 Pair          | AB23 | J8, P8   |

| LPDDR4_CH1_CK_C_A0  | LPDDR4 Clock Device 0 Pair          | AC23 | J9, P9   |

| LPDDR4_CH1_CKE_A0   | LPDDR4 Clock Enable Input           | AB27 | J4, P4   |

| LPDDR4_CH1_CS_A0    | LPDDR4 Chip Select Input            | Y27  | H4, R4   |

Table 3 - LPDDR4 U24 Connections

**NOTE:** The VE2302 SOM requires the end-user carrier card to provide a **SYSTEM CLOCK** that the LPDDR4 interfaces leverages. This **SYSTEM CLOCK** is provided to the LPDDR4 triplet via the JX1 connector. The **SYSTEM CLOCK** provided by the end-user carrier card should be **200MHz LVDS**. Please refer to the **Clock Sources** section of this document for implementation details of the **SYSTEM CLOCK**.

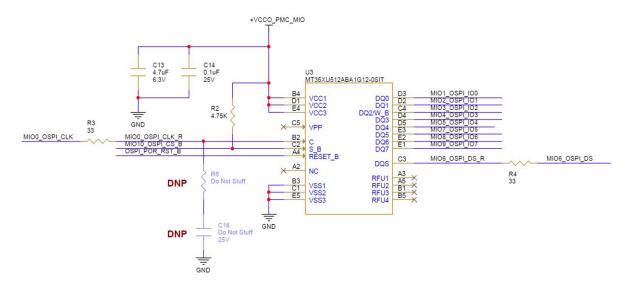

#### 2.2.2 Octal SPI Flash

The VE2302 SOM features one 8-bit OSPI (octal-SPI) serial NOR flash device. The Micron MT35XU512ABA1G12-0AAT OSPI Flash device is used on the VE2302 SOM. The Multi-I/O SPI Flash memory is used to provide non-volatile boot, application code, and data storage. The OSPI Flash can be used as a Boot Device providing 256MB of overall storage and is selectable as the Primary Boot Device via setting the MODE pins appropriately.

The Octal-SPI Flash connects to the PMC OSPI interface via Bank 500. This requires connection to specific pins in MIO Bank 500 and operated at 1.8V I/O, specifically MIO[0:10] and MIO12 as outlined in the <u>AM011</u> (Versal<sup>™</sup> Adaptive SoC Technical Reference Manual).

NOTE: The OSPI interface can be operated up to 150MHz which may be dependent on the operating mode, the performance of the OSPI controller, and the physical implementation of the design (tested with ES1 silicon). This differs from the available published maximum performance of the OSPI controller which supports performance up to 200MHz. It is important when implementing the OSPI controller interface in the AMD design tools to set the performance of the OSPI controller to 150MHz for ES1 silicon. This is expected to be resolved with production silicon. The intent is that the interface operates at 200MHz.

Figure 3 – OSPI Circuit

| Signal Name      | Description            | Bank 500<br>SoC Pin | МІО    | OSPI Pin |

|------------------|------------------------|---------------------|--------|----------|

| MIO0_OSPI_CLK    | OSPI Serial Clock      | AA1                 | MIO_0  | B2       |

| MIO1_OSPI_IO0    | OSPI Data [0]          | AB1                 | MIO_1  | D3       |

| MIO2_OSPI_IO1    | OSPI Data [1]          | AD1                 | MIO_2  | D2       |

| MIO3_OSPI_IO2    | OSPI Data [2]          | AE1                 | MIO_3  | C4       |

| MIO4_OSPI_IO3    | OSPI Data [3]          | AF1                 | MIO_4  | D4       |

| MIO5_OSPI_IO4    | OSPI Data [4]          | AG1                 | MIO_5  | D5       |

| MIO6_OSPI_DS     | OSPI Data Strobe       | AH2                 | MIO_6  | C3       |

| MIO7_OSPI_IO5    | OSPI Data [5]          | AG2                 | MIO_7  | E3       |

| MIO8_OSPI_IO6    | OSPI Data [6]          | AE2                 | MIO_8  | E2       |

| MIO9_OSPI_IO7    | OSPI Data [7]          | AD2                 | MIO_9  | E1       |

| MIO10_OSPI_CS_B  | OSPI Chip Select Input | AC2                 | MIO_10 | C2       |

| MIO12_OSPI_RST_B | OSPI Reset Input       | AA3                 | MIO_12 | A4       |

Table 4 – Octal-SPI Flash Pin Assignment and Definitions

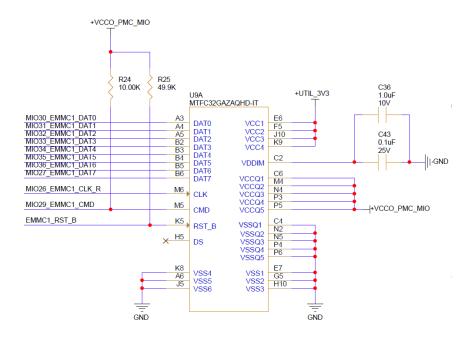

#### 2.2.3 eMMC Flash

The VE2302 SOM provides 32GB of eMMC Flash to be used as a storage device. A single Micron MTFC32GAZAQHD IT (153-pin VFBGA package) device is used to implement the eMMC Flash x8 interface. The eMMC device is connected to the PMC MIO bank 501 and operated at 1.8V I/O. The eMMC I/O has direct connections to the XCVE2302 MIO through the PMC MIO[26:27] and PMC\_MIO[29:36] pins.

The VE2302 SOM end-user can issue a soft reset, **P0\_EMMC1\_RST\_B**, to the eMMC flash device via an on board two-wire serial interface. The active low reset is assigned to Port 0 of the Onsemi **FXL6408UMX** I/O expander. The I/O expander is attached to an I2C peripheral on the VE2302 device. For further

information on the I/O expander and its connections, please refer to the I2C 8-Bit I/O Expander section of this hardware user guide.

Figure 4 – eMMC Circuit

**NOTE:** Not shown in eMMC Circuit are pullup resistors on the data lines between the VE2302 device and the eMMC device.

| Signal Name      | Description      | Bank 501<br>SoC Pin | МІО    | OSPI Pin |  |

|------------------|------------------|---------------------|--------|----------|--|

| MIO26_EMMC1_CLK  | EMMC Clock       | AA5                 | MIO_26 | M6       |  |

| MIO27_EMMC1_DAT7 | EMMC Data IO [7] | AB5                 | MIO_27 | B6       |  |

| MIO29_EMMC1_CMD  | EMMC Command     | AD5                 | MIO_29 | M5       |  |

| MIO30_EMMC1_DAT0 | EMMC Data IO [0] | AE6                 | MIO_30 | A3       |  |

| MIO31_EMMC1_DAT1 | EMMC Data IO [1] | AD6                 | MIO_31 | A4       |  |

| MIO32_EMMC1_DAT2 | EMMC Data IO [2] | AB6                 | MIO_32 | A5       |  |

| MIO33_EMMC1_DAT3 | EMMC Data IO [3] | AA6                 | MIO_33 | B2       |  |

| MIO34_EMMC1_DAT4 | EMMC Data IO [4] | AB7                 | MIO_34 | В3       |  |

| MIO35_EMMC1_DAT5 | EMMC Data IO [5] | AC7                 | MIO_35 | B4       |  |

| MIO36_EMMC1_DAT6 | EMMC Data IO [6] | AD7                 | MIO_36 | B5       |  |

Table 5 - eMMC Pin Assignment and Definitions

#### 2.2.4 SFVA784 Device Package Delay Compensation for Memory Interfaces

The VE2302 SOM device package delay is accommodated for in the layout of the each of the memory interfaces via adjustments in their signal trace lengths. The average of min and max values for package delay is utilized to compensate for the flight time caused by the delay associated with this package.

#### 2.3 GTYP Transceiver Interface

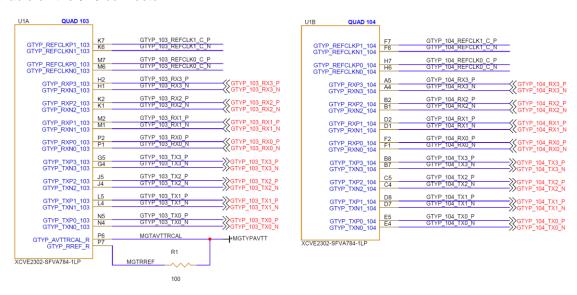

The VE2302 SOM provides 8 GTYP transceivers along with 4 differential reference clocks that reside on Quad 103 and Quad 104 of the XCVE2302 device. These transceivers can be used to interface to multiple high speed interface protocols. Examples of such interfaces are SFP28 and HDMI 2.1. The listed interfaces have reference circuits provided via the Tria Technologies Versal™ AI Edge Carrier Card. The GTYP interfaces are not limited to those listed here as custom interfaces can be created on an end user carrier card.

The GTYP transceivers in the Versal™ architecture are power-efficient transceivers, supporting line rates from 1.25 Gb/s to 32.75 Gb/s depending on the device speed, temperature, and power grades. By default, the VE2302 SOM is populated with a -1LP device. Please refer to the AM002 (Versal™ Adaptive SoC GTY and GTYP Transceivers Architecture Manual) for more information on how each GTYP transceiver can be utilized in a design.

Four (4) differential MGT reference clock inputs are available to support the GTYP transceiver lanes. The multi-gigabit transceiver lanes and their associated reference clocks are connected to the end user carrier card via the JX3 connector. The end user carrier card is responsible for sourcing the proper reference clocks to the VE2302 SOM. Please refer to the Versal<sup>™</sup> AI Edge Series Data Sheet (**DS958**) for the requirements of these reference clocks. As an example, refer to the Versal<sup>™</sup> AI Edge Carrier Card for a solution to providing the GTH reference clocks to the VE2302 SOM.

Each of the VE2302 SOM Quads are length tuned from the XCVE2302 device to the JX3 connector incorporating the device package delays. The device package delay report provided by AMD and the PCB net length report provided by Tria Technologies can be used to determine the required delay for each implemented interface on the end-user carrier card. If the implemented interface is wider than x4 (a single quad), it is imperative to length tune the wider implemented interface on the end user carrier card incorporating each length across the multiple Quads.

**NOTE:** The GTYP transceiver power rails (**+MGTYPAVCC**, **+MGTYPVCCAUX**, and **+MGTYPAVTT**) must be supplied by the carrier card via the JX2 and JX3 connectors. Please refer to the **Power Supplies** section of this document for more information.

The following figure and table show the VE2302 SOM GTYP data and GTYP reference clock input pins available on the JX3 connector.

Figure 5 - GTYP Quad 103 and 104 Connections

| Signal Name        | Pin Number | JX3 Connector |

|--------------------|------------|---------------|

| GTYP_104_REFCLK0_P | H7         | A7            |

| GTYP_104_REFCLK0_N | H6         | A8            |

| GTYP_104_REFCLK1_P | F7         | B10           |

| GTYP_104_REFCLK1_N | F6         | B11           |

| GTYP_104_TX0_P     | E5         | B23           |

| GTYP_104_TX0_N     | E4         | B24           |

| GTYP_104_TX1_P     | D8         | A14           |

| GTYP_104_TX1_N     | D7         | A15           |

| GTYP_104_TX2_P     | C5         | A20           |

| GTYP_104_TX2_N     | C4         | A21           |

| GTYP_104_TX3_P     | B8         | B17           |

| GTYP_104_TX3_N     | B7         | B18           |

| GTYP_104_RX0_P     | F2         | D23           |

| GTYP_104_RX0_N     | F1         | D24           |

| GTYP_104_RX1_P     | D2         | C20           |

| GTYP_104_RX1_N     | D1         | C21           |

| GTYP_104_RX2_P     | B2         | D17           |

| GTYP_104_RX2_N     | B1         | D18           |

| GTYP_104_RX3_P     | A5         | C14           |

| GTYP_104_RX3_N     | A4         | C15           |

| GTYP_103_REFCLK0_P | M7         | C7            |

| GTYP_103_REFCLK0_N | M6         | C8            |

| GTYP_103_REFCLK1_P | K7         | D10           |

| GTYP_103_REFCLK1_N | K6         | D11           |

| GTYP_103_TX0_P     | N5         | B35           |

| GTYP_103_TX0_N     | N4         | B36           |

| GTYP_103_TX1_P     | L5         | A32           |

| GTYP_103_TX1_N     | L4         | A33           |

| GTYP_103_TX2_P     | J5         | B29           |

| GTYP_103_TX2_N     | J4         | B30           |

| GTYP_103_TX3_P     | G5         | A26           |

| GTYP_103_TX3_N     | G4         | A27           |

| GTYP_103_RX0_P     | P2         | D35           |

| GTYP_103_RX0_N     | P1         | D36           |

| GTYP_103_RX1_P     | M2         | C32           |

| GTYP_103_RX1_N     | M1         | C33           |

| GTYP_103_RX2_P | K2 | D29 |

|----------------|----|-----|

| GTYP_103_RX2_N | K1 | D30 |

| GTYP_103_RX3_P | H2 | C26 |

| GTYP_103_RX3_N | H1 | C27 |

Table 6 – Quad 103 and 104 GTYP Pin Assignments

# 2.3.1 SFVA784 Device Package Delay Compensation for GTYP Transceiver Interfaces

The VE2302 SOM device package delay is accommodated for in the layout of the each of the GTYP transceiver signal trace lengths. The average of min and max values for package delay is utilized to compensate for the flight time caused by the delay associated with this package.

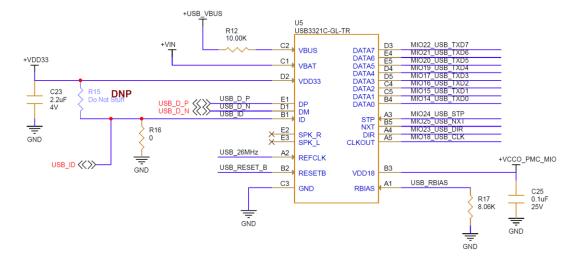

#### 2.4 USB 2.0 PHY

The AMD Versal™ AI Edge device contains a hardened PMC USB 2.0 controller. The VE2302 SOM takes advantage of the PMC USB 2.0 controller to provide USB 2.0 On-The-Go signaling to the JX1 connector.

An external PHY with an 8-bit ULPI interface is implemented. A Microchip **USB3321C** Standalone USB Transceiver Chip is used as the PHY. The PHY features a complete HS-USB Physical Front End supporting speeds of up to 480Mbs. VDDIO for this device can be 1.8V or 3.3V, and on the VE2302 SOM VDDIO is powered at 1.8V. The PHY is connected to PMC MIO Bank 500 which is also powered at 1.8V. This is critical since a level translator cannot be used as it would impact the ULPI timing between the PHY and the XCVE2302 SoC device.

Figure 6 – USB2.0 Circuit

Additionally, the USB3321C must clock the ULPI interface which requires a 26 MHz crystal or oscillator (configured as ULPI Output Clock Mode). On the VE2302 SOM, the 26 MHz oscillator is an ECS CMOS oscillator, ECS-2016MV-260-BN-TR.

The physical USB connector is not populated on the VE2302 SOM. The SOM is designed to have the physical USB connector reside on the end-user carrier card. The three USB connector signals (USB\_D\_P,

**USB\_D\_N** and **USB\_ID**) and **USB\_VBUS** are connected to the JX1 Micro Header. The table below shows the connections of these signals at JX1.

| Signal Name | JX1 Pin |

|-------------|---------|

| USB_D_P     | D29     |

| USB_D_N     | D30     |

| USB_ID      | B30     |

| +USB_VBUS   | D12     |

Table 7 – USB2.0 PHY JX1 Pin Assignments

The USB peripheral is connected through PMC MIO [13-25] in MIO Bank 500 and operated at 1.8V. The USB Reset signal is active-low and signal is connected to PMC MIO[13] to soft reset the USB 2.0 ULPI PHY.

| Signal Name | Description                 | SoC Bank     | MIO         | OSPI Pin |

|-------------|-----------------------------|--------------|-------------|----------|

| DATA[7:0]   | USB Data lines              | MIO Bank 500 | 14:17,19:22 | D[7:0]   |

| CLKOUT      | USB Clock                   | MIO Bank 500 | 18          | A5       |

| DIR         | ULPI DIR output signal      | MIO Bank 500 | 23          | A4       |

| STP         | ULPI STP input signal       | MIO Bank 500 | 24          | А3       |

| NXP         | ULPI NXT output signal      | MIO Bank 500 | 25          | B5       |

| DP          | DP pin of USB Connector     | N/C          | N/C         | E1       |

| DM          | DM pin of USB Connector     | N/C          | N/C         | D1       |

| ID          | ID pin of the USB connector | N/C          | N/C         | B1       |

| RESET_B     | Soft Active-Low Reset       | MIO Bank 500 | 13          | B2       |

Table 8 – ULPI Pin Assignment and Definitions

#### 2.4.1 SFVA784 Device Package Delay Compensation for USB2.0 Interfaces

The VE2302 SOM device package delay is accommodated for in the layout of the USB2.0 signal trace lengths. The average of min and max values for package delay is utilized to compensate for the flight time caused by the delay associated with this package.

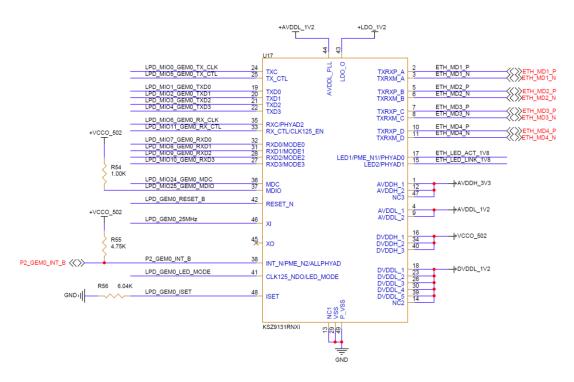

#### 2.5 Ethernet PHY

The VE2302 SOM provides a single Gigabit Ethernet PHY interface using the Microchip **KSZ9131RNXI** RGMII PHY device in 48-pin QFN package (in industrial temp). The VE2302 SOM takes advantage of an LPD GEM controller to provide RGMII Ethernet signaling from Bank 502 to the Gigabit Ethernet PHY. The Gigabit Ethernet PHY physical side (connected to the JX1 connector) along with an RJ45 connector located on an end-user carrier card will be used to implement the Gigabit Ethernet port.

Figure 7 - Ethernet PHY Circuit

The Microchip **KSZ9131RNXI** RGMII Ethernet PHY host side I/O is connected to the LPD MIO bank 502 and operated at 1.8V on the VE2302 SOM. GPIO Port 1 of the I2C 8-bit I/O expander can be used to soft reset the Gigabit Ethernet PHY while P2 port of this I/O expander will be used for the Gigabit Ethernet PHY Interrupt (INT) output. Please refer to the **I2C 8-Bit I/O Expander** section of this document for more information.

The physical RJ45 connector and magnetics are not populated on the VE2302 SOM. The SOM is designed to have the physical RJ45 connector and magnetics reside on the end-user carrier card. The RJ45 connector signals are connected to the JX1 Micro Header. The table below shows the connections of these signals to the JX1 Micro Header:

| Signal Name | JX1 Pin |

|-------------|---------|

| ETH_MD1_P   | D32     |

| ETH_MD1_N   | D33     |

| ETH_MD2_P   | C32     |

| ETH_MD2_N   | C33     |

| ETH_MD3_P   | B32     |

| ETH_MD3_N   | B33     |

| ETH_MD4_P   | A32     |

| ETH_MD4_N   | A33     |

| ETH_ACT     | A29     |

| ETH_LINK    | A30     |

Table 9 – Ethernet PHY JX1 Pin Assignments

On board an end-user carrier card or within the RJ45 Ethernet Jack on the end-user carrier card could be two Ethernet PHY controlled LEDs. The VE2302 SOM provides LINK SPEED and ACTIVITY signals to the on-board RJ45 Ethernet Jack through an OPEN-DRAIN circuit. When implementing these as LEDs on an end-user carrier card the signals should be pulled up to the appropriate voltage such that it will be enough to illuminate the LEDs in an RJ45 jack or other on-board LED circuitry.

The following table shows the pin assignments to Bank 502 of the XCVE2302 device for the RGMII signals.

| Signal Name           | SoC Pin |

|-----------------------|---------|

| LPD_MIO25_GEM0_MDIO   | Y9      |

| LPD_MIO24_GEM0_MDC    | Y8      |

| LPD_MIO11_GEM0_RX_CTL | Y3      |

| LPD_MIO10_GEM0_RXD3   | V3      |

| LPD_MIO9_GEM0_RXD2    | U3      |

| LPD_MIO8_GEM0_RXD1    | Т3      |

| LPD_MIO7_GEM0_RXD0    | U2      |

| LPD_MIO6_GEM0_RX_CLK  | V2      |

| LPD_MIO5_GEM0_TX_CTL  | W2      |

| LPD_MIO4_GEM0_TXD3    | Y2      |

| LPD_MIO3_GEM0_TXD2    | Y1      |

| LPD_MIO2_GEM0_TXD1    | W1      |

| LPD_MIO1_GEM0_TXD0    | U1      |

| LPD_MIO0_GEM0_TX_CLK  | T1      |

| P1_GEM0_RST_B         | N/C     |

Table 10 - Ethernet RGMII Pin Assignments

#### 2.5.1 SFVA784 Device Package Delay Compensation for Ethernet Interface

The VE2302 SOM device package delay is accommodated for in the layout of the Ethernet PHY signal trace lengths. The average of min and max values for package delay is utilized to compensate for the flight time caused by the delay associated with this package.

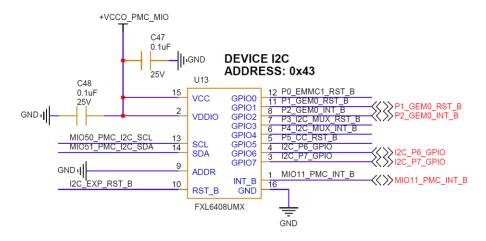

#### 2.6 I2C 8-Bit I/O Expander

The VE2302 SOM uses a ONSemi **FXL6408UMX** (16-pin UMLP) I2C Low-Power I/O Expander for generating various resets and control signals on the VE2302 SOM. The I2C 8-bit I/O expander device is connected to the PMC I2C bus (PMC bank 501 MIO[50:51]) and operated at 1.8V. The interrupt output (**INT\_B**) of the I2C I/O expander device is connected to the PMC\_MIO[11] (Bank 500). The reset input (**RST\_B**) of the I2C I/O expander device has soft reset capabilities and is connected to PMC MIO[28] (Bank 501).

Figure 8 – I2C I/O Expander Circuit

| IO Name | TRM Signal Name | Net Name          |

|---------|-----------------|-------------------|

| SCL     | SCL_OUT         | MIO50_PMC_I2C_SCL |

| SDA     | SDA_OUT         | MIO51_PMC_I2C_SDA |

Table 11 - I2C TRM Pin Mapping

The following tables describes the connections and functionality of the ports of the I2C I/O Expander.

| I/O Expander Name | I/O Expander Pin | Function     | Net Name            |

|-------------------|------------------|--------------|---------------------|

| INT_B             | 1                | INTERRUPT    | MIO11_PMC_INT_B     |

| VDDIO             | 2                | VOLTAGE REF  | +VCCO_PMC_MIO       |

| GPIO7             | 3                | P-PORT       | I2C_P7_GPIO         |

| GPIO6             | 4                | P-PORT       | I2C_P6_GPIO         |

| GPIO5             | 5                | P-PORT       | P5_CC_RST_B         |

| GPIO4             | 6                | P-PORT       | P4_I2C_MUX_INT_B    |

| GPIO3             | 7                | P-PORT       | P3_I2C_MUX_RST_B    |

| GPIO2             | 8                | P-PORT       | P2_GEM0_INT_B       |

| ADDR              | 9                | ADDRESS      | GND                 |

| RST_B             | 10               | RESET        | MIO28_I2C_EXP_RST_B |

| GPIO1             | 11               | P-PORT       | P1_GEM0_RST_B       |

| GPIO0             | 12               | P-PORT       | P0_EMMC1_RST_B      |

| SCL               | 13               | SERIAL CLOCK | MIO50_PMC_I2C_SCL   |

| SDA               | 14               | SERIAL DATA  | MIO51_PMC_I2C_SDA   |

| VCC               | 15               | POWER        | +VCCO_PMC_MIO       |

| GND               | 16               | GROUND       | GND                 |

Table 12 - ONSemi FXL6408UMX Pin Mapping

**NOTE**: On power-up all I/O expander ports default to inputs. With the on-board pull-ups on all ports, all output reset signals shown in the following table will be in their inactive state.

| IO Name | Function                         | Direction | Active-State | Net Name         |

|---------|----------------------------------|-----------|--------------|------------------|

| GPIO0   | eMMC soft reset                  | OUTPUT    | LOW          | P0_EMMC1_RST_B   |

| GPIO1   | Gigabit Ethernet PHY soft reset  | OUTPUT    | LOW          | P1_GEM0_RST_B    |

| GPIO2   | Gigabit Ethernet PHY Interrupt   | INPUT     | LOW          | P2_GEM0_INT_B    |

| GPIO3   | 2-Ch I2C Switch/Mux Reset        | OUTPUT    | LOW          | P3_I2C_MUX_RST_B |

| GPIO4   | 2-Ch I2C Switch/Mux Interrupt    | INPUT     | LOW          | P4_I2C_MUX_INT_B |

| GPIO5   | Carrier Card Reset               | OUTPUT    | LOW          | P5_CC_RST_B      |

| GPIO6   | General Purpose IO – Port 6 (JX) | OUTPUT    | LOW          | I2C_P6_GPIO      |

| GPIO7   | General Purpose IO – Port 7 (JX) | OUTPUT    | LOW          | I2C_P7_GPIO      |

#### Table 13 – IO Expander Pin Functions and Definitions

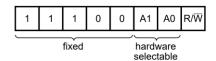

The following figure describes the addressing required to access the I2C I/O Expander. Please see the appropriate device datasheet for further details regarding accessing this device for read and write transactions.

| Name           | ADDR Pin | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Device Address | ADDR = 0 | 1     | 0     | 0     | 0     | 0     | 1     | 1     | WR    |

|                | ADDR = 1 | 1     | 0     | 0     | 0     | 1     | 0     | 0     | WR    |

Figure 9 - I2C I/O Expander Addressing

#### 2.6.1 Carrier Card I2C Expander GPIO Pins

The I2C I/O expander provide 2 GP (General Purpose) I/O pins for use on end-user carrier cards. These I2C driven general purpose pins are routed to the JX1 connector and can be used to implement any interface that does not demand high performance. These GPIO ports are open-drain and require pull-ups be implemented on the end-user carrier card. Please refer to the **FXL6408UMX** device datasheet for the supported voltages on the GPIO ports of the I2C I/O expander.

The following table shows the carrier card I2C expander GPIO pins available on the JX1 connector.

| Signal Name | JX1 Pin Number |

|-------------|----------------|

| I2C_P6_GPIO | C18            |

| I2C_P7_GPIO | C19            |

Table 14 – IO Expander GPIO PIN Assignments

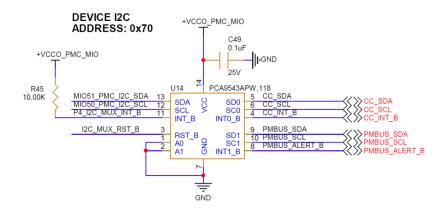

#### 2.7 2-Channel I2C Switch

The VE2302 SOM uses an NXP **PCA9543APW,118** (14-pin TSSOP) I2C Bus Switch with Interrupt connected on the PMC I2C bus (PS bank 501 MIO[50:51]). The use of this I2C switch provides isolation so that devices connected to the I2C bus on the VE2302 SOM, the I2C slave devices on an end-user carrier card, as well as end-user carrier card voltage regulators connected to the PMBus I2C are not physically placed on the same I2C bus.

Figure 10 – 2 Channel I2C Switch Circuit

The following table shows the connections to the PCA9543A device.

| IO Name | TRM Signal Name | Net Name          |

|---------|-----------------|-------------------|

| SCL     | SCL_OUT         | MIO50_PMC_I2C_SCL |

| SDA     | SDA_OUT         | MIO51_PMC_I2C_SDA |

Table 15 - I2C TRM Pin Mapping

The **PCA9543A** may also be used for voltage translation, allowing the use of different bus voltages on each SD/SC pair such that 1.8V, 2.5V, or 3.3V devices can communicate with the 1.8V PMC I2C bus. This is achieved by using external pull-up resistors to pull the isolated bus up to the desired voltage for the master and each slave channel. To support the differing voltage levels, the **PCA9543A** VCC is connected to a 2.5V voltage rail. Please refer to the **PCA9543A** datasheet for more information.

| I/O Expander Name | I/O Expander Pin | Function      | Net Name          |

|-------------------|------------------|---------------|-------------------|

| A0                | 1                | ADDRESS       | GND               |

| A1                | 2                | ADDRESS       | GND               |

| RST_B             | 3                | RESET         | P3_I2C_MUX_RST_B  |

| INT0_B            | 4                | INTERRUPT0    | CC_INT_B          |

| SD0               | 5                | SERIAL DATA0  | CC_SDA            |

| SC0               | 6                | SERIAL CLOCK0 | CC_SCL            |

| GND               | 7                | GROUND        | GND               |

| INT1_B            | 8                | INTERRUPT1    | PMBUS_ALERT_B     |

| SD1               | 9                | SERIAL DATA1  | PMBUS_SDA         |

| SC1               | 10               | SERIAL CLOCK1 | PMBUS_SCL         |

| INT_B             | 11               | INTERRUPT     | P4_I2C_MUX_INT_B  |

| SCL               | 12               | SERIAL CLOCK  | MIO50_PMC_I2C_SCL |

| SDA               | 13               | SERIAL DATA   | MIO51_PMC_I2C_SDA |

| VCC               | 14               | POWER         | +UTIL_2.5V        |

Table 16 - ONSemi PCA9543A Pin Mapping

**NOTE**: GPIO3 port of the I2C 8-bit I/O expander can be used to soft reset the 2-channel I2C switch device. The following table shows how each **PCA9543A** channel will be used. SC1/SD1 should have inline jumpers implemented on an end-user carrier card to allow the PMBUS interface from the VE2302 SOM to be isolated from the circuit preventing multiple master bus contention in the case where an end-user may use an I2C dongle and third-party software to program and / or access the PMBUS regulators in-circuit. Please review the hardware user guide for the Versal<sup>TM</sup> AI Edge Carrier Card for an example implementation.

| I2C Switch Channel                | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                              | Note                                                          |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Master Channel<br>(SDA/SCL/INT)   | This channel is connected to the PMC I2C port, MIO [51:50] and operated at 1.8V. The master <b>INT_N</b> output is connected to the P4 GPIO port of the I2C 8-bit I/O expander.                                                                                                                                                                                                                                                                    | Pulled-up to 1.8V<br>On the SOM                               |

| Slave Channel 0<br>(SD0/SC0/INT0) | This channel is connected to the JX1 connector (CC_SDA, CC_SCL, and CC_INT_N signals) to allow slave I2C devices on an end-user carrier card to be virtually placed on the same PMC I2C bus (MIO [51:50]) as the I2C devices on the VE2302 SOM so that software can use a single PMC I2C bus to communicate will I2C devices through-out the system. Please refer to the Carrier Card I2C Interface section of this document for more information. | Pulled-up to<br>1.8V, 2.5V, or 3.3V<br>On the Carrier<br>Card |

| Slave Channel 1<br>(SD1/SC1/INT1) | This channel is connected to JX1 connector (PMBUS_SDA and PMBUS_SCL signals) used to control all PMBus voltage regulators on end-user carrier cards. This feature allows the PMC I2C to control/monitor the PMBus voltage regulators used on end-user carrier cards for the purpose of power management and/or measurement. Please refer to the PMBus Interface section of this document for more information.                                     | Pulled-up to<br>1.8V, 2.5V, or 3.3V<br>On the Carrier<br>Card |

#### Table 17 - I2C Switch Channel Usage

The following figure describes the addressing required to access the I2C Switch. Please see the appropriate device datasheet for further details regarding accessing this device for read and write transactions.

Figure 11 – I2C Switch Addressing

#### 2.7.1 Carrier Card I2C Interface

The VE2302 SOM provides a master two-wire serial bus (CC\_SDA, CC\_SCL, and CC\_INT\_B) to the end-user carrier card via the JX1 connector so that software can communicate with all I2C devices on the VE2302 SOM as well as the slave I2C devices on the end-user carrier card using a single two-wire serial interface.

The end-user carrier card two-wire serial interface is connected to channel 0 of the 2-channel I2C switch. End-user carrier cards can drive the INT0\_B of the channel 0 via C\_INT\_B, if they so desire. The CC\_INT\_B (an active low signal) is not specific to the I2C interface and can be used as a general-purpose interrupt from end-user carrier cards to the VE2302 SOM. If not used, the CC\_INT\_B signal is to be pulled up to 1.8V, 2.5V, or 3.3V on the carrier card. Since the channel 0 I2C bus is dedicated to the end-user carrier card, two-wire serial devices with any address can reside on this bus without conflicting with the I2C devices on the VE2302 SOM.

| Switch Pin Name | Switch Pin | Function      | Net Name | JX1 Connector |

|-----------------|------------|---------------|----------|---------------|

| INT0_B          | 4          | INTERRUPT0    | CC_INT_B | JX1.A25       |

| SD0             | 5          | SERIAL DATA0  | CC_SDA   | JX1.C29       |

| SC0             | 6          | SERIAL CLOCKO | CC_SCL   | JX1.B25       |

**Table 18 – Carrier Card I2C Net Mapping**

#### 2.7.2 PMBUS Interface

A PMBus can be used with the VE2302 SOM to program/control/monitor all on-board PMBus voltage regulators on an end-user carrier card. The VE2302 SOM has access to the end-user carrier card PMBus signals via the JX1 connector (PMBUS\_SDA, PMBUS\_SCL, and PMBUS\_ALERT\_B signals).

After the initial programming of all PMBus voltage regulators, the VE2302 SOM can utilize the PMBus (via channel 1 and interrupt1 of the I2C switch) to control/monitor the PMBus voltage regulators on the end-user carrier card for the purpose of power management and/or measurement.

| PMBUS Name    | JX1 Connector |

|---------------|---------------|

| PMBUS_SDA     | JX1.B28       |

| PMBUS_SCL     | JX1.C30       |

| PMBUS_ALERT_B | JX1.A26       |

Table 19 – PMBUS JX1 Connector Mapping

Please review the hardware user guide for the Versal<sup>™</sup> Al Edge Carrier Card for an example implementation of the PMBus.

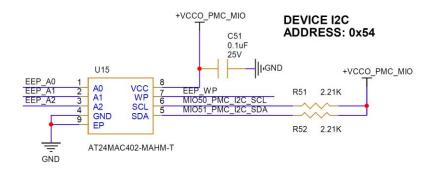

#### 2.8 I2C MAC EEPROM

The VE2302 SOM uses a Microchip **AT24MAC402-MAHM** (8-pin UDFN package) I2C EEPROM 2Kbit 1MHz device. The EEPROM device is connected to the PMC I2C bus (PS bank 501 MIO[50:51]) and operated 1.8V. This device contains a unique EUI-48 ethernet MAC address for solutions that utilize the on-board ethernet and it can be used to store system level parameters/data.

Figure 12 – I2C EEPROM Circuit

| IO Name  | TRM Signal Name | Net Name          |

|----------|-----------------|-------------------|

| PS_MIO50 | SCL_OUT         | MIO50_PMC_I2C_SCL |

| PS_MIO51 | SDA_OUT         | MIO51_PMC_I2C_SDA |

Table 20 - I2C TRM Pin Mapping

The following table describes the connections to the I2C EEPROM.

| EEPROM Name | EEPROM Pin | Function         | Net Name          |

|-------------|------------|------------------|-------------------|

| A0          | 1          | ADDRESS INPUT    | GND               |

| A1          | 2          | ADDRESS INPUT    | GND               |

| A2          | 3          | ADDRESS INPUT    | +VCCO_PMC_MIO     |

| GND         | 4          | GROUND           | GND               |

| SDA         | 5          | SERIAL ADDR/DATA | MIO51_PMC_I2C_SDA |

| SCL         | 6          | SERIAL CLOCK     | MIO50_PMC_I2C_SCL |

| WP          | 7          | WRITE PROTECT    | GND               |

| VCC         | 8          | POWER            | +VCCO_PMC_MIO     |

Table 21 - Microchip AT24MAC402 Pin Mapping

The following figure describes the addressing required to access the I2C EEPROM. Please see the appropriate device datasheet for further details regarding transactions to and from this device.

| Access Area               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| EEPROM                    | 1     | 0     | 1     | 0     | A2    | A1    | A0    | R/W   |

| EUI or Serial Number Read | 1     | 0     | 1     | 1     | A2    | A1    | A0    | 1     |

| Write-Protect Registers   | 0     | 1     | 1     | 0     | A2    | A1    | A0    | R/W   |

Figure 13 – EEPROM I2C Addressing

#### 2.9 User IO Pins

#### 2.9.1 Processor MIO User Pins

The VE2302 SOM provides 13 end-user PMC MIO pins directly from Bank 501 and 12 end-user LPD MIO pins from Bank 502 to the JX1 Connector. The 25 MIO pins connect to the Adaptive SoC Processor Sub-System for the implementation of peripherals such as USB, SPI, SDIO, CAN, UART, and I2C. These I/O pins can also be used as general purpose I/O to connect push buttons, LEDs and/or switches to the VE2302 SOM from an end-user carrier card.

The VCCO for Bank 501 and Bank 502 is generated on the VE2302 SOM and set to +1.8V and is names **+VCCO\_PMC\_MIO**. This voltage rail is also provided on the JX1 connector pin A24 so that it may be utilized on circuits associated with the MIO pins on an end-user carrier card.

**NOTE:** The Bank 501 PMC MIO and Bank 502 LPD MIO connections to the JX1 connector are provided in a master table that documents all the JX Connections of the VE2302 SOM. Please refer to the **Expansion Headers** section of this document.

#### 2.9.2 Programmable Logic IO User Pins

The VE2302 SOM provides 22 user HDIO pins from Bank 302, 28 user XPIO pins from bank 702 and 52 user XPIO pins from Bank 703 of the Versal<sup>™</sup> Adaptive SoC. The 102 PL IO pins on the VE2302 SOM connect to the Programmable Logic Sub-System for user implementation of most any feasible interface.

Bank 302 provides 22 user HDIO (High Density) pins. These pins are routed to the JX1 connector and are available to implement peripherals on end-user custom carrier cards. The HDIO bank 302 pins can be operated between 1.8V and 3.3V. The bank voltage **+VCCO\_302** is to be provided by the end-user carrier card via the JX1 connector. Please refer to the **Expansion Headers** section of this document for the location of the **+VCCO\_302** pins on the JX1 connector. Please refer to **Power Supplies** section of this document for the power/sequencing requirements for bank 302 power rail.

The bank 302 HDIO pins are routed with matched lengths to the JX1 connectors. The matched pairs may be used as either single ended I/O or differential pairs depending on the end users design requirements. See the **VE2302 SOM Net Length** report for more details on the matched lengths to the JX1 connector.

Banks 702 and 703 provide 80 XPIO (High Performance) pins. These pins are routed to the JX2 connector and are available to implement peripherals on end-user custom carrier cards. The XPIO bank 702 and 703 pins can be operated between 1.0 to 1.5V. The bank voltages +VCCO\_702 and +VCCO\_703 are to be provided by the end-user custom carrier card via the JX2 connector. Please refer to the Expansion Headers section of this document for the location of the +VCCO\_702 and +VCCO\_703 pins on the JX2 connector. Please refer to Power Supplies section of this document for the power/sequencing requirements for the bank 702 and bank 703 power rails.

The bank 702 and bank 703 XPIO pins are routed with matched lengths to the JX2 connectors. The matched lengths differ here from bank 302 as the matching of lengths are done by AMD nibbles which are 6-pins. Each nibble within bank 702 and bank 703 is length matched. The matched pairs may be used as either single ended I/O or differential pairs depending on the end users design requirements. See the **VE2302 SOM Net Length** report for more details on the matched lengths to the JX2 connector.

It is recommended that any custom interface to be designed and run through the Vivado tool suite for a sanity check on place and route and timing closure in advance of end-user carrier card manufacturing.

**NOTE:** The bank 302 HDIO and bank 702 and 703 XPIO connections to the JX connectors are provided in a master table that documents all the JX Connections of the VE2302 SOM. Please refer to the **Expansion Headers** section of this document.

#### 2.9.3 SFVA784 Device Package Delay Compensation for User I/O Interfaces

The VE2302 SOM device package delay is accommodated for in the layout of the User I/O interface signal trace lengths. The average of min and max values for package delay is utilized to compensate for the flight time caused by the delay associated with this package.

#### 2.10 Clock Sources

The VE2302 SOM provides a 33.333MHz +/-10ppm single-ended 1.8V reference clock source to the PMC configuration Bank 503 **REF\_CLK** input to act as a system reference clock. An **ECS-2520SMV-333.3-FN-TR** with 33-ohm series termination is used.

The VE2302 SOM can provide a Real-Time Clock (RTC). A 32.768 kHz crystal is connected to the PMC Configuration Bank 503 RTC\_PADI and RTC\_PADO pins for the RTC. The on-chip RTC uses the +VCC\_BATT pin (provided by the end-user carrier card via the JX1 connector) for the backup battery. End user carrier cards will drive the +VCC\_BATT pin with an appropriate battery if this functionality is required.

| MIO Name | Package Pin Number | Net Name  | JX1 Connector |

|----------|--------------------|-----------|---------------|

| RTC_PADI | AH7                | RTC_PADI  | -             |

| RTC_PADO | AH8                | RTC_PADO  | -             |

| VCC_BATT | W15                | +VCC_BATT | JX1.D27       |

Table 22 - RTC Crystal Pin Assignments

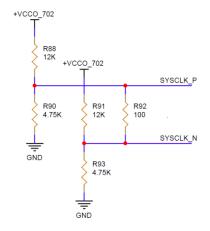

The VE2302 SOM requires the end-user carrier card to provide a **SYSTEM CLOCK** that the LPDDR4 interfaces leverages. This **SYSTEM CLOCK** is provided to the LPDDR4 triplet via the JX1 connector. The **SYSTEM CLOCK** provided by the end-user carrier card should be **200MHz LVDS**. An example of the **SYSTEM CLOCK** is provided by the Versal<sup>™</sup> AI Edge Carrier Card. Please refer to the **Versal<sup>™</sup> AI Edge Carrier Card Hardware User Guide** for the example implementation of SYSTEM CLOCK.

| Net Name | Package Pin Number | JX1 Connector |

|----------|--------------------|---------------|

| SYSCLK_P | Bank 702 - N23     | JX1.D14       |

| SYSCLK_N | Bank 702 - N24     | JX1.D15       |

Table 23 – LPDDR4 System Clock Pin Assignments

The VE2302 SOM does provide termination for the SYSTEM CLOCK differential pair. The following figure shows the termination provided on the VE2302 SOM.

Figure 14 – SYSCLK Provided Termination

#### 2.11 Control Signal Sources

#### 2.11.1 Power-On Reset (POR) Control Signal

The Power-On Reset (POR\_B) circuit for the AMD Versal<sup>™</sup> AI Edge device is required to be implemented on the end-user carrier card. The POR\_B is an active-low input signal to the AMD Versal<sup>™</sup> AI Edge device that acts as a master reset. The signal name associated with POR\_B port on the AMD Versal<sup>™</sup> AI Edge device is SOM\_RESET\_IN\_B and that signal is provided on the JX2 connector (Pin JX2-B32). The VE2302 SOM does provided a 10K-ohm pull-up to +VCCO\_PMC\_MIO (1.8V) on SOM\_RESET\_IN\_B. See the Versal<sup>™</sup> AI Edge Carrier Card Hardware User Guide for an example implementation of SOM\_RESET\_IN\_B control.

The external reset, **SOM\_RESET\_IN\_B**, can reset the end-user carrier card thru an open drain signal on the JX2 connector, **CC\_RESET\_OUT\_B**. The VE2302 SOM is also capable of issuing a soft reset by asserting Port 5 of the I2C I/O Expander, **P5\_CC\_RST\_B**, to the end-user carrier card using the VE2302 SOM two-wire serial interface. This will soft reset the end-user carrier card thru the same open drain signal on the JX2 connector (**Pin JX2-C14**), **CC\_RESET\_OUT\_B**. See the **I2C 8-bit I/O Expander** section of this document for details regarding Port 5 of the I2C I/O Expander.

The following table is a list of the locations on the JX2 connecter of the power-on reset control signals.

| Control Signal Name | JX2 Connector | Voltage            | Active-State |

|---------------------|---------------|--------------------|--------------|

| SOM_RESET_IN_B      | JX2-B32       | +1.8V (SOM)        | Low          |

| CC_RESET_OUT_B      | JX2-C14       | Open-Drain to User | Low          |

Table 24 – Power-On Reset Control Pin Assignments

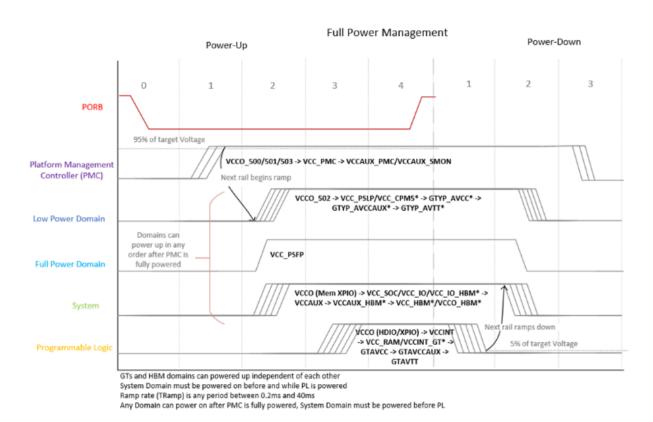

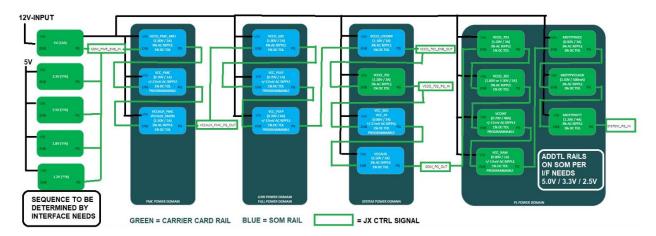

#### 2.11.2 Power Supply Sequencing Control Signals

An end-user carrier card should design the on-board power solution to account for the bring up time of the individual power supplies and devise a method to ensure that power is valid prior to the release of POR\_B control signal and the booting of the AMD Versal™ AI Edge device. The end-user carrier card is required to use the SOM\_PWR\_ENB\_IN, VCCO\_702\_ENB\_OUT, VCCO\_702\_PG\_IN, and SOM\_PG\_OUT signals to control the bring-up and sequencing of the on-board power supplies. System overall power good should meet the time required for all power rails to be stable listed in the Versal™ AI Edge datasheet (DS958).

**SOM\_PWR\_ENB\_IN** is the control signal used to enable the **POWER SEQUENCER** on the VE2302 SOM. This signal is required to be pulled up to +3.3V on the end-user carrier card. On the Versal<sup>™</sup> AI Edge Carrier Card, this signal is enabled after the always-on regulators are stable which includes the VE2302 SOM +VIN rail of +5V.

VCCO\_702\_ENB\_OUT is a control signal pulled up to +3.3V that is generated by the **POWER SEQUENCER** which informs the end user carrier card to enable the voltage regulator used to generate +VCCO\_702. This is used to maintain the proper sequencing for the AMD Versal™ AI Edge device.

When the power for **+VCCO\_702** is stable, the end user carrier card should assert **VCCO\_702\_PG\_IN** back to the VE2302 SOM. This signal is required to be pulled up to +3.3V on the end-user carrier card.

When the power supplies on the VE2302 SOM are stable the **SOM\_PG\_OUT** will be asserted to +3.3V to the end-user carrier so that the remaining power supplies on that platform can be brought up in the proper sequence.

More details regarding the use of the power control signals listed here are provided in the **Power Supplies** section of this document. Please also refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** and the **Versal™ Al Carrier Card Design Guide** for details regarding the implementation of the proper system power sequencing.

The following table is a list of the locations on the JX connecters of the power supply sequencing control signals.

| Control Signal Name | JX2 Connector | Voltage         | Active-State |

|---------------------|---------------|-----------------|--------------|

| SOM_PWR_ENB_IN      | JX2-C32       | +3.3V (Carrier) | High         |

| VCCO_702_ENB_OUT    | JX2-C8        | +3.3V (SOM)     | High         |

| VCCO_702_PG_IN      | JX2-D8        | +3.3V (Carrier) | High         |

| SOM_PG_OUT          | JX1-B29       | +3.3V (SOM)     | High         |

Table 25 – Power Supply Sequencing Control Pin Assignments

#### 2.11.3 PUDC\_B Control Signal and Status Signals

**PUDC\_B** by default has a pull-up resistor to the appropriate voltages applied. The **PUDC\_B** does have a footprint available such that you can remove the pull-up and populated the secondary resistor and pull the **PUDC\_B** signal to GND. **PUDC\_B** is the pull-up during configuration pin that is used to select the behavior of the XPIO/HDIO during configuration. The default setting on the VE2302 SOM is HIGH, which means the XPIO and HDIO are put into tri-state mode. If **PUDC\_B** is LOW then internal pull-ups would be enabled on the XPIO and HDIO during configuration.

DONE and ERROR OUT are configuration status signals from the AMD Versal™ AI Edge device bank 503. The DONE signal is a bidirectional pin that is an open-drain signal with a weak internal pull-up resistor. DONE is tri-stated and pulled HIGH when the BOOT sequence is complete. The ERROR\_OUT signal is an output pin that is an open-drain signal with a weak internal pull-up resistor. ERROR\_OUT is tri-stated and pulled HIGH when an error occurs in the AMD Versal™ AI Edge device. The end user carrier card can use these status signals to illuminate on-board LEDs to show BOOT sequence complete or that an error occurred. Please refer to the Versal™ AI Edge Carrier Card Hardware User Guide for details regarding the implementation of these status signals.

The following table is a list of the locations on the JX1 connecter of the bank 503 configuration status signals.

| Control Signal Name | JX1 Connector | Voltage              | Active-State |

|---------------------|---------------|----------------------|--------------|

| DONE                | JX1-D28       | Open-Drain (Carrier) | High         |

| ERROR_OUT           | JX1-D13       | Open-Drain (Carrier) | High         |

Table 26 – Configuration Status Signal Pin Assignments

#### 2.11.4 On-Board Peripheral Reset Control

The VE2302 SOM provides resets control signals to the various peripherals on the SOM via PMC MIO pins or through the I2C 8-bit I/O expander. All reset controls signals are active-LOW. The reset operation for the peripherals connected to the VE2302 SOM are as follows:

- OPSI This device is reset via POR\_B or the PMC MIO[12] signal.

- USB 2.0 ULPI PHY This device is reset via POR B or the PMC MIO[13] signal.

- I2C 8-Bit I/O Expander This device is reset via POR B or the PMC MIO[28] signal.

- eMMC Device This device is reset via POR\_B or GPIO0 port of the I2C 8-bit I/O expander.

- Gigabit Ethernet PHY This device is reset via POR\_B or GPIO1 port of the I2C 8-bit I/O expander.

- 2-Channel I2C Switch This device is reset via POR B or GPIO3 port of the I2C 8-bit I/O expander.

- Carrier Card Reset The carrier card is reset via POR\_B or GPIO5 port of the I2C 8-bit I/O expander.

#### 2.12 Expansion Headers

#### 2.12.1 Micro Headers

The VE2302 SOM features three Micro Headers for connection to end-user carrier cards. The three Micro Headers consist of 160-pin connectors from Samtec, ADF6-40-03.5-L-4-0-A. These connectors are Samtec 0.635mm AcceleRate® HD High Density 4-Row Sockets with 160 Positions and have stack heights options from 5mm and 16mm, making it easy to connect to a variety of expansion or system boards depending on the end-user requirements. By default, the mating solution with the Versal™ AI Edge Carrier Card is set to 5mm. Each pin can carry 1.340A of current and support I/O speeds more than what the AMD Versal™ AI Edge device can deliver with performance up to 64Gbps PAM4.