## AUBoard-15P Development Kit Getting Started Guide

Version 1.3

Page 1 Copyright © 2025 TRIA Technologies. TRIA is a registered trademark of Avnet, Inc. All other brands are the property of their respective owners. LIT# AUB-15P-DK-GSG-V1P1

## Contents

| 1 | Document Control5               |                                                                                                  |                                  |  |  |

|---|---------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| 2 | Version History5                |                                                                                                  |                                  |  |  |

| 3 | Pertinent Info6                 |                                                                                                  |                                  |  |  |

| 3 | 3.1                             | What's In The Box                                                                                | .7                               |  |  |

| 3 | 3.2                             | What's On The Web                                                                                | .8                               |  |  |

| 3 | 3.3                             | Available Documentation                                                                          | .8                               |  |  |

| 3 | 3.4                             | Tutorials and Reference Designs                                                                  |                                  |  |  |

| 3 | 3.5                             | Trainings and Videos                                                                             | .8                               |  |  |

|   |                                 |                                                                                                  |                                  |  |  |

| 4 |                                 | tting Started                                                                                    |                                  |  |  |

| • |                                 |                                                                                                  | .9                               |  |  |

| 2 | Ge                              | tting Started                                                                                    | .9<br>9                          |  |  |

| 2 | Get<br>1.1                      | tting Started<br>Out-of-Box Example Design                                                       | .9<br>9<br>9                     |  |  |

| 2 | Get<br>1.1<br>1.2               | tting Started<br>Out-of-Box Example Design<br>Hardware Setup                                     | .9<br>9<br>9<br>11               |  |  |

| 2 | Get<br>4.1<br>4.2<br>4.3        | tting Started.<br>Out-of-Box Example Design<br>Hardware Setup<br>Terminal Setup                  | .9<br>9<br>9<br>11<br>12         |  |  |

|   | Get<br>4.1<br>4.2<br>4.3<br>4.4 | tting Started.<br>Out-of-Box Example Design<br>Hardware Setup<br>Terminal Setup<br>Boot FreeRTOS | .9<br>.9<br>.9<br>11<br>12<br>13 |  |  |

## **Figures**

| Figure 1 – Development Kit Block Diagram      | 6  |

|-----------------------------------------------|----|

| Figure 2 – Interfaces and Connectors          | 7  |

| Figure 3 – Cable Locations on AUBoard-15P     | 11 |

| Figure 4 – USB-JTAG/UART COM Port Assignments | 11 |

| Figure 5 – Out-of-Box Design Boot             | 12 |

| Figure 6 – Out-of-Box Design Web Server Page  | 13 |

| Figure 7 – Webserver Board Control Interfaces | 13 |

## 1 Document Control Document Version:

| Document Date: | 14 January 2025 |

|----------------|-----------------|

1.1

## 2 Version History

| Version | Date       | Comment                        |

|---------|------------|--------------------------------|

| 1.0     | 10/28/2024 | Initial Release                |

| 1.1     | 01/14/2025 | Updated with production photos |

| 1.2     | 02/05/2025 | Updated Website Links          |

| 1.3     | 06/10/2025 | Updated AMD Branding and temp  |

## **3 Pertinent Info**

The AUBoard-15P Development Kit is a solution that incorporates an AMD Artix<sup>™</sup> UltraScale+<sup>™</sup> on a PCIe Gen4 x4 board targeted for broad use in many applications:

- Offers an AMD based Development Kit for engineers to adopt in development, proof-of-concept, and production projects.

- Combines programmable logic designs with a MicroBlaze soft microprocessor core in a convenient and expandable board.

- Allows expansion to a variety of sensors and peripherals through the Mikroe Click Board<sup>™</sup> and FMC (FPGA Mezzanine Card) expansion connectors.

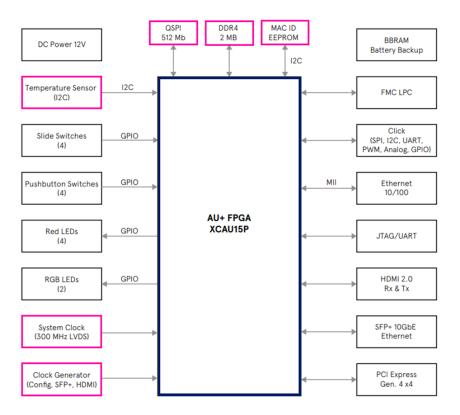

The following figure is a high-level block diagram of the AUBoard-15P Development Kit and the peripherals attached to the Artix UltraScale+ FPGA.

## Figure 1 – Development Kit Block Diagram

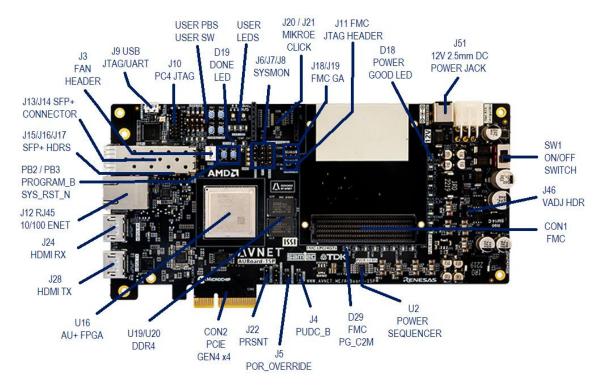

The following figure provides an overview of the physical connections, their designators, and relative position on the AUBoard-15P Development Kit. This image is of the production version of the AUBoard-15P Development Kit but the components depicted are still in there relevant locations.

## Figure 2 – Interfaces and Connectors

The Getting Started Guide will outline the steps to setup the AUBoard-15P Development Kit hardware and documents the procedure to run the Out-of-Box FreeRTOS.

#### 3.1 What's In The Box

The AUBoard-15P Development Kit includes the AUBoard-15P PCIe Gen4 x4 board. The AUBoard-15P Development Kit includes the following in the box:

- AUBoard-15P PCIe Gen4 x4 board

- Power Supply

- Quick Start Card

- PCIe Bracket

Customers may need to acquire a micro-B USB cable, Ethernet cable, SFP+ cable, and HDMI cables depending on their end application. Customers will also need to procure or produce appropriate modules that target the various expansion interfaces. Here are links to web pages that provide such products:

- MikroE Click Boards: <u>https://www.mikroe.com/click</u>

- FMC: https://www.xilinx.com/products/boards-and-kits/fmc-cards.html

This is not an exhaustive list of available off-the-shelf products targeting the expansion connectors but should provide a user an idea of the available products that could be leveraged.

## 3.2 What's On The Web

The AUBoard-15P Development Kit has documentation that is made available to users through the Avnet Board product page, element14, and Hackster.io community websites. Here are links to the various online content:

- http://avnet.me/auboard-15p

- <u>http://avnet.me/auboard-15p-forum</u>

- <u>http://avnet.me/board-support-site</u>

## 3.3 Available Documentation

- Getting Started Guide

- Hardware User Guide

- Board Definition Files

- Master User Constraint File

- Net Length Report

- Schematics \*

- Bill of Materials \*

- Mechanical Drawing \*

- 3D Model \*

- Source Databases \*\*

\* Denotes FAE involvement to gain access to these documents. Contact your local Avnet FAE. \*\* Denotes FAE involvement and execution of Non-Disclosure Agreement (NDA). Contact your local Avnet FAE.

#### 3.4 Tutorials and Reference Designs

Any tutorials and reference designs that are available to targets this platform can be located at the links below.

- FreeRTOS Out-of-Box Design

- MicroBlaze RISC-V Petalinux Design

- HDMI Pass-Thru Example Design

- Avnet Boards Training and Courses

- o http://avnet.me/tria-boards-training

#### 3.5 Trainings and Videos

Any trainings and videos that may be available to target this platform can be located at the links below.

- Community based boards trainings and videos

- http://avnet.me/community-boards-training

## 4 Getting Started

The functionality of the AUBoard-15P Development Kit is determined by the application configured from the non-volatile memory. In the case of the AUBoard-15P Development Kit the main configuration option is the on-board QSPI. For this Getting Started tutorial, the Out-of-Box image has been programmed into the QSPI at the factory. Having the QSPI pre-programmed allows the end user to quickly bring up the board with a network connection and run an application built using FreeRTOS.

Reminder: In addition to the items included in the box, you will also need the following to complete the Getting Started tutorial.

- Micro-B USB Debug Cable for USB-UART Communications

- Open Ethernet Port on Network Router or Network Switch

- Ethernet Cable

## 4.1 Out-of-Box Example Design

The AUBoard-15P Development Kit has a FreeRTOS design that is utilized as its Out-of-Box experience. This FreeRTOS design is programmed to the on-board QSPI at the factory. Here is a link to the FreeRTOS Out-of-Box design that could alternatively be used when configuring the FPGA via JTAG.

<u>http://avnet.me/auboard-15p-dk-oob</u>

#### 4.2 Hardware Setup

There are a few tasks required to ensure the hardware is setup appropriately to run the Out-of-Box FreeRTOS design.

1) Check that the appropriate headers are shunted on the AUBoard-15P Development Kit.

The first header to review is the VCCO\_66\_86 voltage select header, **J46**, which determines if the voltage placed on VCCO Bank 66 and VCCO Bank 86. This voltage select header, **J46**, is used to select +1.8V or +1.2V for the +VCCO\_66\_86 rail on the AUBoard-15P Development Kit.

- For +VCCO\_66\_86 to be set to +1.8V by shunting pin 1 to pin 2 on **J46**.

- For +VCCO\_66\_86 to be set to +1.2V do not place a shunt on **J46**.

The second set of headers to review is the PUDC\_B header, **J4**, and the POR\_OVERRIDE header, **J5**. The PUDC\_B header controls the state of the SelectIO from power-on until configuration completes on the AMD Artix<sup>™</sup> UltraScale+<sup>™</sup> device. The POR\_OVERRIDE header controls the power-on reset delay before configuration begins for the Artix UltraScale+ device.

- For PUDC\_B header **J4** not shunted pulls up this signal disabling internal pull-up resistors on SelectIO pins. SelectIO will be 3-stated after-power when PUDC is high.

- For PUDC\_B header **J4** shunted pin 1 to pin 2 pulls down the PUDC\_B signal enabling internal pull-up resistors on SelectIO pins.

- For POR\_OVERRIDE header J5 shunted pin 1 to pin 2 pulls up this signal shortening the power-on-delay as specified in the Artix UltraScale+ data sheet. Note: Header J5 should be shunted.

- For POR\_OVERRIDE header **J5** shunted pin 3 to pin 2 pulls down this signal elongating the power-on-delay. **Note: Header J5 should be shunted.**

- Note: POR\_OVERRIDE J5 should be default shunted pin 3 to pin 2 connecting POR\_OVERRIDE to GND unless the flash will always be ready as soon as the FPGA is powered up.

The next header to review is the FMC JTAG header, **J11**, and the FMC General Address (**GA0/GA1**) headers, **J18** and **J19**. The FMC header controls the inclusion of the FMC JTAG signals into the JTAG chain. The FMC General Address headers sets the I2C addresses on the FMC Mezzanine Card.

- For FMC JTAG header **J11** shunted pin 1 to pin 2 the JTAG chain will only include the FPGA and cards plugged into the FMC header may not be visible to the JTAG chain.

- For FMC JTAG header **J11** shunted pin 3 to pin 2 the JTAG chain will include both the FPGA and any devices on the JTAG chain that are included on the FMC card plugged into the FMC connector, **CON1**.

- Header **J18** and **J19** can be pulled high by shunting from pin 1 to pin 2 or can be pulled low by shunting from pin 3 to pin 2.

The last header to review is the MAC ID EEPROM Write Protect header, **J23**. The MAC ID EEPROM Write Protect header when enabled prevents write accesses from corrupting the MAC ID EEPROM contents.

- For MAC ID EEPROM Write Protect header **J23** shunted pin 1 to pin 2 pulls up the Write Protect function and it will be enabled on the MAC ID EEPROM.

- For MAC ID EEPROM Write Protect header **J23** shunted pin 3 to pin 2 pulls down the Write Protect function and writes to the MAC ID EEPROM can occur.

# Note: This list calls out important headers and may not document all available options. Please review the AUBoard-15P Development Kit User Guide for the full list of header documentation.

- 2) The appropriate cables should be attached to the AUBoard-15P Development Kit. The cables required to run the Out-Of-Box design are as follows:

- Ethernet Cable should be attached from host PC ethernet interface to the AUBoard-15P Development Kit RJ45 connector, **J12**.

- microUSB Cable should be attached from host PC USB interface to the AUBoard-15P USB JTAG/UART connector, **J9**.

- Attach the provided barrel jack power supply (or connect board to a powered PCIe Card Edge) to the AUBoard-15P Development Kit Power Supply connector, **J51**.

The following figure depicts the fully connected AUBoard-15P Development Kit ready to run the Out-of-Box Design. The image depicted here is a production version of the AUBoard-15P Development Kit.

Figure 3 – Cable Locations on AUBoard-15P

## 4.3 Terminal Setup

- 1) A terminal program is required. Tera Term was used in this example which can be downloaded from the Tera Term project. Install Tera Term or another terminal program of your choice to a host Windows PC.

- <u>https://teratermproject.github.io/index-en.html</u>

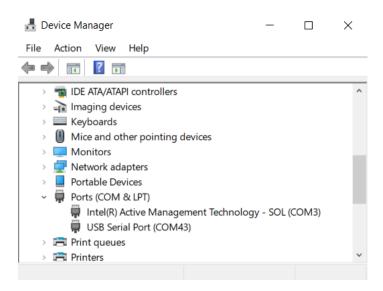

- 2) When a microUSB cable is connected to the AUBoard-15P Development Kits USB JTAG/UART port J9 from your host Windows PC with the board having been powered on by toggling switch SW1 to ON, the proper drivers, if installed, will give you confirmation of the available COM ports in the Device Manager of Windows as show in the following figure.

Figure 4 – USB-JTAG/UART COM Port Assignments

- If the drivers are not installed, then you must manually install the driver for the FT2232H device. Visit the FTDI website and download the appropriate driver for your operating system.

- <u>http://www.ftdichip.com/Drivers/VCP.htm</u>

- 4) Prior to installing drivers manually, you should power off the board by toggling switch SW1 to off and then unplug the microUSB cable from the AUBoard-15P Development Kit. After the Kit is unplugged from the PC you can unzip and install the FT2232H driver.

- 5) At this point you should reboot your PC and then proceed to plug in the microUSB cable for the USB JTAG/UART to **J9**.

## 4.4 Boot FreeRTOS

Prior to booting the FreeRTOS Out-of-Box Example Design, we need to ensure that the network connection that we are using for this design is setup properly for ethernet communication to occur.

For the Out-of-Box Design to function properly we need to have the IP address of the AUBoard-15P Development Kit set by a DHCP server. The assignment of the IP address should automatically be accomplished on most networks using a Network Router or Network Switch.

With the AUBoard-15P Development Kit setup and the IP address able to be assigned automatically by the DHCP server, it is now time to boot the FreeRTOS Out-of-Box Design on the AUBoard-15P Development Kit by toggling switch **SW1** to ON. The board will start to boot and complete with terminal appearing as follows:

```

COM9 - Tera Term VT

\times

File Edit Setup Control Window KanjiCode Help

AU15P Board SPI Flash Bootloader v1.0 Build on Oct 15 2024

Boot application AU15P_OOB.elf

. .

AUBoard-15P OOB Program

leys task start running

---lwIP Socket Mode Demo Application -----

XEMacLite detect_phy: PHY detected at address 1.

auto-negotiated Tink speed: 100

DHCP request success

MAC Address: FC:C2:3D:4A:F8:26

IP Address : 192.168.1.44

Netmask : 255.255.255.0

: 192.168.1.1

Gateway

http server is running on port 80

'lease point your web browser to <u>http://192.168.1.44</u>

```

## Figure 5 – Out-of-Box Design Boot

## 4.5 Using Out-of-Box Example Design

At this point, it is time to utilize the Out-of-Box Example Design. Open your favourite web browser and point the browser to the assigned IP address displayed in the terminal window.

If everything has been successful to this point, the user will see the following web page in the web browser:

## Figure 6 – Out-of-Box Design Web Server Page

In the webpage GUI, the user will be able to toggle the USER RGB LEDs (**D35 and D36**) of the AUBoard-15P Development Kit showing communication and control over ethernet of the board. The user will be able to set toggle the USER LEDs ON and OFF via buttons in the **LED TAB** of the webpage. The user will also be able to toggle the USER SWITCH **SW2** values and read them back via the GUI.

| Changing LEDs                                      | Reading Switch         |

|----------------------------------------------------|------------------------|

| RGB LED D35 Blue Set LED RGB LED D36 Green Set LED | Read Switch Value 0000 |

#### Figure 7 – Webserver Board Control Interfaces

On board, the user will be able to toggle the various User Push Buttons on the board (**PB4, PB5, PB6, and PB7**) which will in turn cause the User RED LEDs (**D31**, **D32**, **D33**, and **D34**) to toggle ON and OFF.

- Pressing PB7 Toggle D34 RED LED.

- Pressing PB6 Toggle D33 RED LED.

- Pressing PB5 Toggle D32 RED LED.

- Pressing PB4 Toggle D31 RED LED.

- Pressing PB2 Will cause the FPGA to reconfigure (PROG\_B control).

## 4.6 Getting Started Complete

That completes this tutorial. The user may now power down the AUBoard-15P Development Kit by toggling power slide switch **SW1** to the off position.

## 5 Getting Help and Support

If additional support is required, TRIA Technologies has many avenues to search depending on your needs.

For general question regarding AUBoard-15P Development Kit, please visit our website at <u>http://avnet.me/auboard-15p</u>. Here you can find any available documentation, technical specifications, videos and tutorials, reference designs and other support.

Detailed questions regarding AUBoard-15P Development Kit hardware design, software application development, using AMD tools, training and other topics can be posted on the AUBoard-15P Development Kit Support Forum at <u>http://avnet.me/auboard-15p-forum</u>. Avnet's technical support team monitors the forum during normal business hours in North America.

Those interested in customer-specific options on AUBoard-15P Development Kit can send inquiries to **customize@avnet.com**.