# **VE2302 SOM Carrier Card Design Guide**

Version 1.2

# **Contents**

| 1 | Dog   | Document Control             |     |  |

|---|-------|------------------------------|-----|--|

| 2 | Ver   | sion History                 | 7   |  |

| 3 | Intr  | oduction                     | 8   |  |

|   | 3.1   | Additional Information       | . 8 |  |

| 4 | VE    | 2302 SOM                     | 9   |  |

| 5 | VE    | 2302 SOM On-Board Resources1 | 1   |  |

| _ | 5.1   | AMD Versal™ AI Edge APSoC    |     |  |

|   | 5.1.  |                              |     |  |

|   | 5.1.2 | 2 PMC MIO Bank 500           | 11  |  |

|   | 5.1.3 | 3 PMC MIO Bank 501           | 11  |  |

|   | 5.1.4 | 4 PMC MIO Bank 502           | 12  |  |

|   | 5.1.  | 5 PMC MIO Bank 503           | 12  |  |

|   | 5.1.6 | S XPIO Bank 700-701          | 12  |  |

|   | 5.1.  | 7 XPIO Bank 702-703          | 12  |  |

|   | 5.1.8 | GTYP Quad Bank 103-104       | 12  |  |

|   | 5.2   | Reference Clock              | 12  |  |

|   | 5.3   | Real-Time Clock              | 12  |  |

|   | 5.4   | I2C MAC EEPROM               |     |  |

|   | 5.5   | I2C 8-Bit IO Expander        | 13  |  |

|   | 5.6   | 2-Channel I2C Switch         |     |  |

|   | 5.7   | LPDDR4 SDRAM                 |     |  |

|   | 5.8   | Octal SPI Flash              |     |  |

|   | 5.9   | eMMC Flash                   |     |  |

|   | 5.10  | USB 2.0 PHY                  |     |  |

|   | 5.11  | Ethernet PHY                 |     |  |

| 6 |       | 2302 SOM External Resources1 |     |  |

|   | 6.1   | SYSMON Header                |     |  |

|   | 6.2   | System Clock                 |     |  |

|   | 6.3   | Boot Mode Interface          |     |  |

|   | 6.4   | JTAG Interface               |     |  |

|   | 6.5   | Status Signals               |     |  |

|   | 6.6   | Power-On Reset               |     |  |

|   | 6.7   | Carrier Card I2C Interface   |     |  |

|   | 6.8   | PMBus Interface              |     |  |

|   | 6.9   | I2C GPIO Expander Ports      |     |  |

|   | 6 10  | LISR2 0 Connector            | 28  |  |

|    | 6.11  | RJ45 GbE Jack                             | 28 |

|----|-------|-------------------------------------------|----|

|    | 6.12  | PMC MIO Interfaces                        | 29 |

|    | 6.13  | LPD MIO Interfaces                        | 30 |

|    | 6.14  | HDIO Interfaces                           | 30 |

|    | 6.15  | XPIO Interfaces                           | 31 |

|    | 6.16  | GTYP Interfaces                           | 33 |

| 7  | Pov   | wer Requirements                          | 34 |

|    | 7.1   | Power-On Reset Timing                     | 36 |

|    | 7.2   | Power Sequencing                          | 36 |

|    | 7.3   | Recommended Carrier Card Power Sequence   | 39 |

| 8  | JX    | Micro Headers                             | 39 |

|    | 8.1   | Mating JX Receptacle Connectors           | 40 |

|    | 8.2   | JX Micro Headers Matched Lengths          | 41 |

|    | 8.3   | JX Connector Master Table                 | 41 |

| 9  | SO    | M Mechanical Dimensions                   | 51 |

| 1  | 0 Car | rrier Card PCB Design Guidelines          | 52 |

|    | 10.1  | Connector Land and Alignment              | 52 |

|    | 10.2  | USB and Ethernet Connector Signal Routing | 52 |

|    | 10.2  | 2.1 Ethernet Connector Pin routing        | 52 |

|    | 10.2  | 2.2 USB Connector Pin routing             | 52 |

|    | 10.3  | GTYP Transceiver Signal Routing           | 52 |

|    | 10.4  | PMC and LPD MIO Routing                   | 53 |

|    | 10.5  | SYSMON Signal Routing                     | 53 |

|    | 10.6  | HDIO and XPIO Signal Routing              | 54 |

|    | 10.7  | JX1, JX2, and JX3 Routing Delays          | 54 |

|    | 10.8  | JTAG Interface Signal Routing             | 60 |

|    | 10.9  | Decoupling Caps                           | 60 |

|    | 10.10 | Mechanical Considerations                 | 60 |

|    | 10.11 | Thermal Considerations                    | 61 |

| 1  | 1 Get | tting Help and Support                    | 61 |

| 1: | 2 Gei | neral Information                         | 61 |

|    | 12.1  | Intended Use                              | 62 |

|    | 12.2  | RoHS Compliance                           | 62 |

|    | 12.3  | Electrostatic Discharge                   | 63 |

|    | 12.4  | Warranty                                  | 63 |

|    |       |                                           |    |

# **Figures**

| Figure 1 – VE2302 SOM Block Diagram                            | 10 |

|----------------------------------------------------------------|----|

| Figure 2 – Example System Clock Schematic                      | 23 |

| Figure 3 –System Clock SOM Termination Schematic               | 23 |

| Figure 4 – Example Boot Mode Switch Schematic                  | 23 |

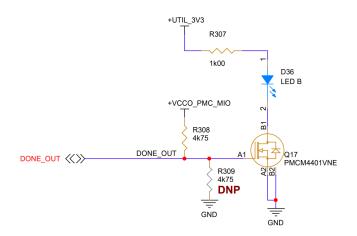

| Figure 5 – DONE_OUT LED Schematic                              | 25 |

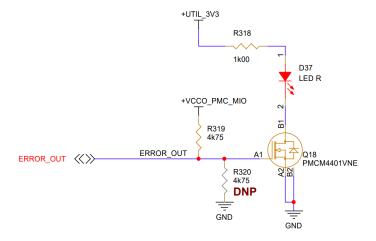

| Figure 6 – ERROR_OUT LED Schematic                             | 25 |

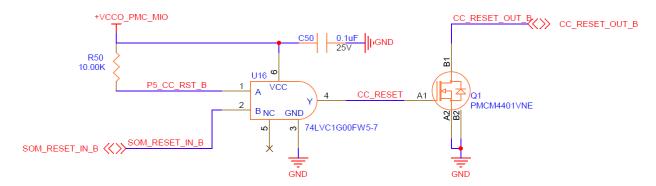

| Figure 7 – Carrier Card Output Reset Circuit                   | 26 |

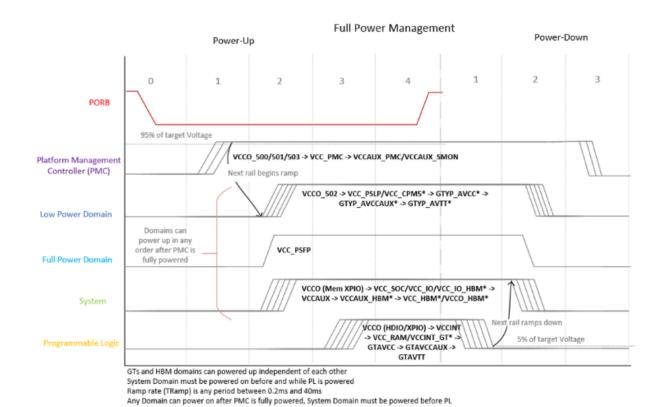

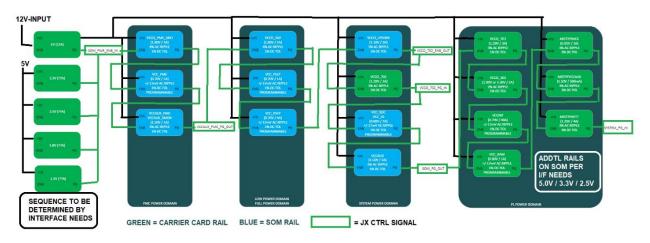

| Figure 8 – Versal Power-On Sequence                            | 37 |

| Figure 9 – Example Power Sequencing with End-User Carrier Card | 37 |

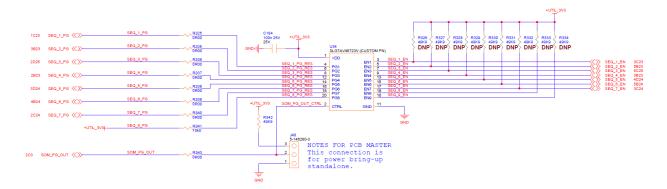

| Figure 10 – Custom Power Sequencer Circuit                     | 38 |

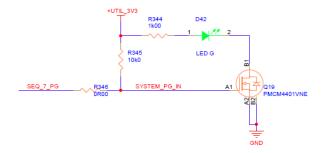

| Figure 11 – System Power Good LED                              | 38 |

| Figure 12 – Connectors mated heights                           | 40 |

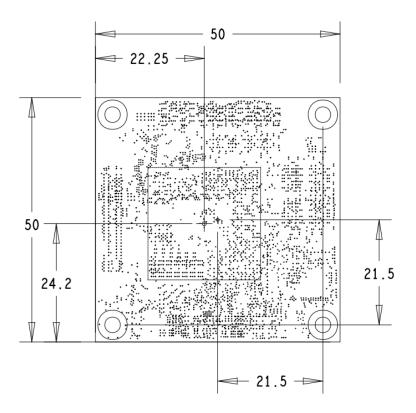

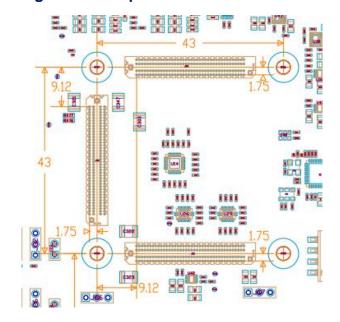

| Figure 13 – Top Mechanical Dimensions                          | 51 |

| Figure 14 – Bottom Mechanical Dimensions                       | 51 |

| Figure 15 – Side Mechanical Dimensions (TBD)                   | 52 |

| Tables                                                         |    |

| Tables                                                         |    |

| Table 1 – Glossary                                             | 8  |

| Table 2 – I2C IO Expander Port Usage                           | 13 |

| Table 3 – I2C Switch Channel Usage                             | 14 |

| Table 4 – Octal SPI Flash Pin Assignments                      | 15 |

| Table 5 – eMMC Flash Interface Pin Assignments                 | 15 |

| Table 6 – ULPI Pin Assignment and Definitions                  | 16 |

| Table 7 – Ethernet RGMII Pin Assignments                       |    |

| Table 8 – Micro Header JX1 Summary                             | 18 |

| Table 9 – Micro Header JX2 Summary                             | 19 |

| Table 10 – Micro Header JX3 Summary                            | 19 |

| Table 11 – VE2302 SOM External Interface Signals               | 22 |

| Table 12 – SYSMON Interface Pin Assignments                    | 22 |

| Table 13 –System Clock Interface Pin Assignments               | 22 |

| Table 14 – Supported Boot Modes                                | 24 |

| Table 15 – Boot Mode Interface Pin Assignments        | 24 |

|-------------------------------------------------------|----|

| Table 16 – JTAG Interface Pin Assignments             | 24 |

| Table 17 – DONE_OUT LED Pin Assignment                | 25 |

| Table 18 – ERROR_OUT LED Pin Assignment               | 25 |

| Table 19 – Power-On Reset Pin Assignments             | 26 |

| Table 20 – Carrier Card I2C Interface Pin Assignments | 27 |

| Table 21 – PMBus Interface Pin Assignments            | 27 |

| Table 22 – IO Expander GPIO PIN Assignments           | 28 |

| Table 23 – USB2.0 PHY JX1 Pin Assignments             | 28 |

| Table 24 – Ethernet PHY JX1 Pin Assignments           | 29 |

| Table 25 – PMC MIO Pin Assignments                    | 29 |

| Table 26 – LPD MIO Pin Assignments                    |    |

| Table 27 – HDIO Pin Assignments                       | 31 |

| Table 28 – XPIO 703 Pin Assignments                   |    |

| Table 29 – XPIO 702 Pin Assignments                   | 33 |

| Table 30 – GTYP Interface Pin Assignments             | 34 |

| Table 31 – VE2302 SOM Power Requirements              | 35 |

| Table 32 – Power Sequencing Control Signals           | 39 |

| Table 33 – JX Micro Header Connectors Pinout Summary  | 43 |

| Table 34 – JX1 Connector Pin-out                      | 46 |

| Table 35 – JX2 Connector Pin-out                      | 48 |

| Table 36 – JX3 Connector Pin-out                      | 50 |

| Table 37 – JX1 Connector Routing Delay                | 55 |

| Table 38 – JX2 Connector Routing Delay                | 58 |

| Table 39 – JX3 Connector Routing Delay                | 59 |

# **1 Document Control**

**Document Version:** 1.2

**Document Date:** 5 August 2025

Document Author(s): Donny Saveski

# **2 Version History**

| Version | Date      | Comment                    |

|---------|-----------|----------------------------|

| 1.0     | 6/13/2025 | Initial Release            |

| 1.1     | 6/30/2025 | Master JX Table Correction |

| 1.2     | 8/5/2025  | Master JX Table Correction |

# 3 Introduction

This document provides guidelines for designing an end-user carrier card for the VE2302 SOM. It includes reference schematics for implementing the VE2302 SOM external peripherals as well as PCB design guidelines for the end-user carrier card.

The following table is a glossary of acronyms that could be used in description of the design guidelines for an end-user carrier card.

| Term   | Definition                      |

|--------|---------------------------------|

| PS     | Adaptive SoC Processing System  |

| PL     | Adaptive SoC Programmable Logic |

| MIO    | Multiplexed Input Output Pins   |

| LPD    | Low Power Domain                |

| PMC    | Platform Manager Controller     |

| PLM    | Platform Loader and Manager     |

| POR    | Power On Reset                  |

| APU    | Application Processing Unit     |

| RPU    | Real-time Processing Unit       |

| GPU    | Graphics Processing Unit        |

| SYSMON | System Monitor                  |

| ADC    | Analog-to-Digital Converter     |

| HDIO   | High Density PL I/O Pins        |

| XPIO   | High Performance PL I/O Pins    |

| PMBus  | Power Management Bus            |

| PDM    | Power Design Manager            |

| ООВ    | Out-of-Box                      |

Table 1 - Glossary

#### 3.1 Additional Information

Additional information and documentation on the AMD Versal™ Adaptive SoC can be found Here: <a href="https://www.amd.com/en/products/adaptive-socs-and-fpgas/versal.html">https://www.amd.com/en/products/adaptive-socs-and-fpgas/versal.html</a>

Additional information and documentation on the Tria Technologies VE2302 SOM product line can be found here: <a href="http://avnet.me/ve2302-som">http://avnet.me/ve2302-som</a>

Additional information and documentation on the Tria Technologies VE2302 Development Kit can be found here: <a href="http://avnet.me/ve2302-dk">http://avnet.me/ve2302-dk</a>

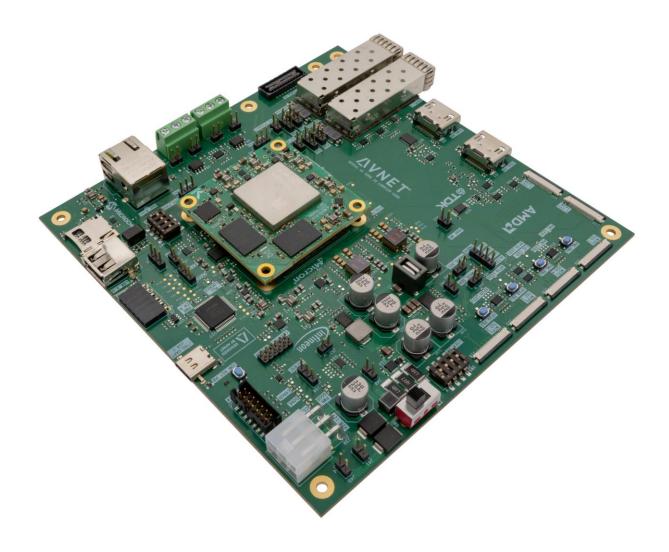

# 4 VE2302 SOM

The Tria Technologies VE2302 SOM (System-On-Module) is a high-performance product targeted for broad use in many applications. The goal of the module is to offer a compact SOM (50mm x 50mm) solution with an AMD Versal™ AI Edge device in commercial (0C to 70C) and industrial (-40C to 85C) temperature grades for engineers to adopt in development, proof-of concept, and production designs. The features provided by the VE2302 SOM consist of:

- AMD XCVE2302-1LSESFVA784 (Pin compatible with the XCVE2202 device)

- Pin compatible with the XCVE2102, XCVE2202, and XCVM1102

- Primary configuration options: OSPI flash

- Auxiliary configuration options via end user carrier card:

- JTAG

- microSD card

- Memory

- o LPDDR4 SDRAM (4GB, 2x32)

- o PMC OSPI Flash (Octal 256MB)

- o PMC eMMC Flash (x8 32GB)

- o I2C MAC EEPROM (2Kb)

- Interfaces

- o PMC USB 2.0 ULPI PHY (Connector required on end user carrier card)

- o Gigabit Ethernet RGMII PHY (Connector required on end user carrier card)

- o I2C 8-bit I/O Expander

- 2-channel I2C Switch/Mux

- 3 JX Micro-Header Connectors (3 x 160-pin)

- 80 User XPIO Pins

- 22 User HDIO Pins

- 12 User LPD MIO Pins

- 13 User PMC MIO Pins

- 8 GTYP Transceivers

- 4 GTYP Reference Clock Inputs

- PMC JTAG Interface

- PMC SYSMON interface

- USB 2.0 Connector Interface

- Gigabit Ethernet RJ45 Connector Interface

- PMBus Interface

- Carrier Card I2C Interface

- SOM +VCC BATT Battery Input

- SOM Reset Input

- Carrier Card Interrupt Input

- Carrier Card Reset Output

- SOM Power Good Output

- SOM to Carrier Card Ground Pins

- SOM Input Voltages and Output Sense Pins

- o Reference Clock

- 33.333 MHz OSC

- o Real Time Clock (RTC)

- Power

- On-Board Voltage Regulators

- Custom Power Sequencer (Supports power-up and power-down sequencing)

- Bank I/O and GTYP Transceiver Voltage Rails (Supplied via end user carrier card)

The following figure is a high-level block diagram of the VE2302 SOM and the peripherals attached to the Adaptive SoC Processing Sub-System and Programmable Logic Sub-System. The interfaces on the VE2302 SOM are divided into processing system (PS) interfaces and programmable logic (PL) interfaces. This document will describe the VE2302 SOM, its on-board resource, and external interface available to carrier cards.

Figure 1 – VE2302 SOM Block Diagram

# 5 VE2302 SOM On-Board Resources

The following sections provide a brief description of each component/resource available on the VE2302 SOM.

# 5.1 AMD Versal™ AI Edge APSoC

The full default part number, XCVE2302-1LSESFVA784, populated on the VE2302 SOM. The VE2302 SOM utilizes the AMD XCVE2302-SFVA784 device in -1 speed grade part (the VE2302 SOM is designed to support all speed grades for the XCVE2302-SFVA784 device with customization). The XCVE2302-SFVA784, supports APU speed up to 1.65GHz, RPU speed up to 750MHz, and LPDDR4 speeds up to 4266Mbps. The XCVE2302-SFVA784 device features the following resources:

- Dual-core Arm®-A72

- Dual-core Arm Cortex-R5F

- 34 Al Engine-ML Tiles

- 328,720 System Logic Cells

- 22 HD (High Density) IO pins (PL bank 302)

- 52 PMC (Platform Management Controller) MIO pins (PS bank 500 and 501)

- 26 LPD (Low Power Domain) MIO pins (PS bank 502)

- 208 XP (High Performance) IO pins (PL banks 700, 701, 702, and 703)

- 8 GTYP transceivers (PL quad 103 and 104)

- 4 GTYP reference clock inputs (PL quad 103 and 104)

- JTAG interface (PS bank 503)

- Real-Time Clock (PS bank 503)

- SYSMON interface (PS bank 500)

The following sections provide brief descriptions of how each XCVE2302 APSoC bank is used on the VE2302 SOM followed by detail descriptions in subsequent sections.

#### 5.1.1 HDIO Bank 302

The HDIO bank 302 provides 22 HD (High Density) IO pins. These pins are routed to the **JX1** connector and are available for use by end-user carrier cards. The HDIO bank pins can be operated at 1.8V through 3.3V. The VCCO voltages for the HDIO bank are provided by the end-user carrier card via the **JX1** connector using **+VCCO\_302** pins.

## 5.1.2 PMC MIO Bank 500

The PMC MIO bank 500 consists of 26 PMC MIO pins, **PMC\_MIO[0:25]\_500**. The PMC MIO pins for this bank are operated at 1.8V and used to implement the following interfaces on the VE2302 SOM:

- Octal SPI Flash

- USB2.0 ULPI PHY Interface

- System Monitor (SMON) pins

#### 5.1.3 PMC MIO Bank 501

The PMC bank 501 consists of 26 PMC MIO pins, **PMC\_MIO[26:51]\_501**. The PMC MIO pins for this bank are operated at 1.8V. 12 of the PMC MIO pins are routed to the **JX1** connector and are available to enduser carrier cards. The other PMC MIO pins in this bank are used to implement the eMMC x8 Flash and PMC I2C interface.

- 12x PMC MIO Routed to JX1 Connector

- eMMC x8 Flash

- I2C MAC ID EEPROM (2Kb)

- I2C 8-Bit I/O Expander

- I2C Bus Switch

#### 5.1.4 PMC MIO Bank 502

The PMC MIO bank 502 consists of 26 MIO pins, **LPD\_MIO[0:25]\_502**. The PMC MIO bank 502 pins are operated at 1.8V. 11 of the PMC MIO pins are routed to the **JX1** connector and are available to end-user carrier cards. The other PMC MIO pins in this bank are used to implement the Gigabit Ethernet RGMII PHY and MDIO interfaces.

#### 5.1.5 PMC MIO Bank 503

The PMC MIO bank 503 is the configuration bank for the Versal<sup>™</sup> AI Edge device. This bank contains the device power-on reset (POR\_B) signal, reference clock, JTAG interface, boot mode pins, status signals ERROR OUT and DONE OUT, and the real-time clock oscillator inputs.

#### 5.1.6 XPIO Bank 700-701

The XPIO banks 700 and 701 consist of the LPDDR4 interface pins. These pins are used on the VE2302 SOM to implement the LPDDR4 2x32 memory interface. The XPIO bank 700 and 701 IO are operated at 1.1V.

#### 5.1.7 XPIO Bank 702-703

The XPIO banks 702 and 703 provides 80 XPIO pins. These pins are routed to the **JX2** connector and are available for use by end-user carrier cards. The XPIO bank pins can be operated at 1.0 through 1.5V. The VCCO voltages for the XPIO banks are provided by the end-user carrier card via the **JX2** connector using the **+VCCO\_702** and **+VCCO\_703** pins.

#### 5.1.8 GTYP Quad Bank 103-104

The GTYP quads 103 and 104 consist of GTYP transceivers and their associated reference clock input pins (Device provides 8 GTYP transceivers along with 4 reference clock inputs). These pins are routed to the **JX3** connector and are available for use by end-user carrier cards.

**NOTE**: The GTYP transceiver power rails (**+MGTYPAVCC**, **+MGTYPAVTT**, and **+MGTYPVCCAUX**) are supplied by the end-user carrier card via the **JX2** and **JX3** connectors.

#### 5.2 Reference Clock

The VE2302 SOM provides a 33.33 MHZ single-ended 1.8V reference clock input to the Versal™ AI Edge APSoC bank 503 **REF\_CLK\_503** pins.

#### 5.3 Real-Time Clock

The Versal™ AI Edge device provides a built-in Real-Time Clock (RTC) function. A 32.768 KHz crystal is connected to the bank 503 RTC\_PADI and RTC\_PADO pins to support the RTC. The on-chip RTC uses the +VCC\_BATT pin, that is to be provided by the end-user carrier card via JX1 connector, for the backup battery.

#### 5.4 I2C MAC EEPROM

The VE2302 SOM provide 2Kb of I2C EEPROM using a Microchip **AT24MAC402-MAHM** (8-pin UDFN package) device. The EEPROM device is connected to the PMC I2C bus (**PMC MIO[50:51]**) and operated with a VCC of 1.8V. This device contains a unique EUI-48 ethernet MAC address for solutions that utilize the on-board ethernet and it can be used to store system level parameters/data.

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the I2C MAC EEPROM.

## 5.5 I2C 8-Bit IO Expander

The VE2302 SOM uses a onSemi **FXL6408UMX** (16-pin UMLP) I2C Low-Power 8-bit IO expander device for generating various resets and control signals on the VE2302 SOM. The I2C 8-bit IO expander device is connected to the PMC I2C bus (**PMC MIO[50:51]**) and operated with a VCC of 1.8V. The interrupt output (**INT#**) of the **FXL6408** device is connected to **PMC MIO[11]**. The following table shows how the I2C 8-bit IO expander ports are utilized.

**NOTE**: On power-up all I/O expander ports default to inputs. With the on-board pull-ups on all ports, all output reset signals shown in the following table will be in their inactive state.

| IO Expander Port | Direction | Usage                            |

|------------------|-----------|----------------------------------|

| GPIO0            | Output    | eMMC soft reset                  |

| GPIO1            | Output    | Gigabit Ethernet PHY soft reset  |

| GPIO2            | Input     | Gigabit Ethernet PHY Interrupt   |

| GPIO3            | Output    | 2-Ch I2C Switch/Mux Reset        |

| GPIO4            | Input     | 2-Ch I2C Switch/Mux Interrupt    |

| GPIO5            | Output    | Carrier Card Reset               |

| GPIO6            | Output    | General Purpose IO – Port 6 (JX) |

| GPIO7            | Output    | General Purpose IO – Port 7 (JX) |

Table 2 – I2C IO Expander Port Usage

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the I2C 8-bit IO Expander.

#### 5.6 2-Channel I2C Switch

The VE2302 SOM uses a 2-channel I2C switch to expand the PMC I2C bus (**PMC MIO[50:51]**). An NXP **PCA9543APW,118** (14-pin TSSOP) device is used for this interface. The use of this I2C switch provides isolation so that devices connected to the I2C bus on the VE2302 SOM and the I2C slave devices on an end-user carrier card, as well as PMBus voltage regulators are not physically placed on the same I2C bus preventing overlap.

The **PCA9543A** may also be used for voltage translation, allowing the use of different bus voltages on each SD/SC pair such that 1.8V, 2.5V, or 3.3V devices can communicate with the PMC bank 501 1.8V I2C MIO pins. This is achieved by using external pull-up resistors to pull the bus up to the desired voltage for the master and each slave channel. The **PCA9543A** has its VCC connected to 2.5V on the VE2302 SOM to support this translation.

**NOTE**: GPIO3 port of the I2C 8-bit IO expander can be used to soft reset the 2-channel I2C switch device. The following table shows how each **PCA9543A** channel is used on the VE2302 SOM.

**NOTE**: An end-user carrier card should place inline jumpers on SC1/SD1 to allow downstream voltage regulators on the PMBus to be removed from circuit. This would allow-end user carrier cards to implement third-part programming headers and avoid contention with the VE2302 SOM.

| I2C Switch Channel                | Usage                                                                                                                                                                                                                                                                                                                                                                                                                  | Note                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Master Channel<br>(SDA/SCL/INT)   | This channel is connected to the PMC I2C port, MIO [51:50] and operated at 1.8V. The master INT_N output is connected to the GPIO4 port of the I2C 8-bit IO expander.                                                                                                                                                                                                                                                  | Pulled-up to 1.8V<br>On the SOM                               |

| Slave Channel 0<br>(SD0/SC0/INT0) | This channel is connected to the JX1 connector (CC_SDA, CC_SCL, and CC_INT_N signals) to allow slave I2C devices on a carrier card to be virtually placed on the same PMC I2C bus (MIO [51:50]) as the I2C devices on the VE2302 SOM so that software can use a single PMC I2C core to communicate with I2C devices in the system.                                                                                     | Pulled-up to<br>1.8V, 2.5V, or 3.3V<br>On the Carrier<br>Card |

| Slave Channel 1<br>(SD1/SC1/INT1) | This channel is connected to the PMBus (PMBUS_SDA and PMBUS_SCL signals) of the VE2302 SOM. It is used to control/monitor PMBus voltage regulators on end-user carrier cards (the PMBus is connected to carrier cards via the JX1 connector).  This feature allows the PMC I2C to control/monitor the PMBus voltage regulators used on end-user carrier cards for the purpose of power management and/or measurements. | Pulled-up to<br>1.8V, 2.5V, or 3.3V<br>On the Carrier<br>Card |

# Table 3 - I2C Switch Channel Usage

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the 2-Channel I2C Switch.

#### 5.7 LPDDR4 SDRAM

The VE2302 SOM provides 4GB of LPDDR4 memory in a 2x32 configuration using 2 Micron MT53E512M32D1ZW-046 IT:B (200-pin BGA package) x32 devices. The LPDDR4 devices are implemented in 512Mb x 32 configuration and supports up to 3200Mbps. The LPDDR4 devices are connected to the XPIO banks 700 and 701 and operated at 1.1V at the maximum supported bandwidth available in the PIN EFFICIENT implementation on the Versal™ AI Edge device.

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the LPDDR4 SDRAM interface.

#### 5.8 Octal SPI Flash

The VE2302 SOM provides 256MB of Octal SPI (OSPI) flash in a single (x8) configuration. One Micron MT35XU512ABA1G12-0AAT OSPI Flash device is used to implement the interface on the VE2302 SOM. The OSPI Flash device is connected to the PMC MIO bank 500 and operated at 1.8V. The OSPI Flash can be used as a primary boot device on the Versal VE2302 SOM. Please refer to the AM011 (Versal Adaptive SoC Technical Reference Manual) for more information.

| Signal Name      | Description            | Bank 500<br>SoC Pin | MIO    |

|------------------|------------------------|---------------------|--------|

| MIO0_OSPI_CLK    | OSPI Serial Clock      | AA1                 | MIO_0  |

| MIO1_OSPI_IO0    | OSPI Data [0]          | AB1                 | MIO_1  |

| MIO2_OSPI_IO1    | OSPI Data [1]          | AD1                 | MIO_2  |

| MIO3_OSPI_IO2    | OSPI Data [2]          | AE1                 | MIO_3  |

| MIO4_OSPI_IO3    | OSPI Data [3]          | AF1                 | MIO_4  |

| MIO5_OSPI_IO4    | OSPI Data [4]          | AG1                 | MIO_5  |

| MIO6_OSPI_DS     | OSPI Data Strobe       | AH2                 | MIO_6  |

| MIO7_OSPI_IO5    | OSPI Data [5]          | AG2                 | MIO_7  |

| MIO8_OSPI_IO6    | OSPI Data [6]          | AE2                 | MIO_8  |

| MIO9_OSPI_IO7    | OSPI Data [7]          | AD2                 | MIO_9  |

| MIO10_OSPI_CS_B  | OSPI Chip Select Input | AC2                 | MIO_10 |

| MIO12_OSPI_RST_B | OSPI Reset Input       | AA3                 | MIO_12 |

Table 4 – Octal SPI Flash Pin Assignments

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the OSPI Flash interface.

#### 5.9 eMMC Flash

The VE2302 SOM provides 32GB of eMMC Flash to be used as a on-board storage. A single Micron MTFC32GAZAQHD IT (153-pin VFBGA package) device is used to implement the eMMC Flash x8 interface. The eMMC device is connected to the PS MIO bank 501 and operated at 1.8V. GPIO0 port of the VE2302 SOM I2C 8-bit IO expander can be used to soft reset the eMMC device.

| Signal Name | MIO Pin Number | Notes        |

|-------------|----------------|--------------|

| CLK         | PMC_MIO26      | eMMC Clock   |

| DATA7       | PMC_MIO27      | eMMC DATA[7] |

| CMD         | PMC_MIO29      | eMMC Command |

| DATA0       | PMC_MIO30      | eMMC DATA[0] |

| DATA1       | PMC_MIO31      | eMMC DATA[1] |

| DATA2       | PMC_MIO32      | eMMC DATA[2] |

| DATA3       | PMC_MIO33      | eMMC DATA[3] |

| DATA4       | PMC_MIO34      | eMMC DATA[4] |

| DATA5       | PMC_MIO35      | eMMC DATA[5] |

| DATA6       | PMC_MIO36      | eMMC DATA[6] |

**Table 5 – eMMC Flash Interface Pin Assignments**

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding of the eMMC flash interface and the use of port 0 of the I2C 8-bit IO Expander as a soft reset.

#### 5.10 USB 2.0 PHY

The VE2302 SOM provides a single USB 2.0 PHY interface using the Microchip **USB3321C** USB 2.0 ULPI PHY in a 25-pin WLCSP package in industrial temperature range. The USB 2.0 ULPI PHY connector side (connected to the **JX1** connector) can be used on end-user carrier cards to implement a USB 2.0 interface with a single connector.

The USB peripheral is connected through **PMC MIO [13-25]** in MIO Bank 500 and operated at 1.8V. The USB Reset signal is active-low and signal is connected to **PMC MIO [13]** to soft reset the USB 2.0 ULPI PHY.

| Signal Name | Description                 | SoC Bank     | MIO         | USB Pin |

|-------------|-----------------------------|--------------|-------------|---------|

| DATA[7:0]   | USB Data lines              | MIO Bank 500 | 14:17,19:22 | D[7:0]  |

| CLKOUT      | USB Clock                   | MIO Bank 500 | 18          | A5      |

| DIR         | ULPI DIR output signal      | MIO Bank 500 | 23          | A4      |

| STP         | ULPI STP input signal       | MIO Bank 500 | 24          | А3      |

| NXP         | ULPI NXT output signal      | MIO Bank 500 | 25          | B5      |

| DP          | DP pin of USB Connector     | N/C          | N/C         | E1      |

| DM          | DM pin of USB Connector     | N/C          | N/C         | D1      |

| ID          | ID pin of the USB connector | N/C          | N/C         | B1      |

| RESET_B     | Soft Active-Low Reset       | MIO Bank 500 | 13          | B2      |

Table 6 – ULPI Pin Assignment and Definitions

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the USB ULPI PHY interface to the **JX1** connector.

#### 5.11 Ethernet PHY

The VE2302 SOM provides a single Gigabit Ethernet PHY interface using the Microchip **KSZ9131RNXU** RGMII PHY device in 48-pin QFN package in industrial temperature range. The VE2302 SOM Gigabit Ethernet PHY connector side (connected to the **JX1** connector) along with an RJ45 GbE jack located on the end-user carrier card will be used to implement the Gigabit Ethernet port.

The Microchip **KSZ9131RNXU** RGMII Ethernet PHY host side IO is connected to the LPD MIO bank 502 and operated at 1.8V. GPIO1 Port of the I2C 8-bit IO expander can be used to soft reset the Gigabit Ethernet PHY while GPIO2 port of the I2C 8-bit IO expander can be used for the Gigabit Ethernet PHY Interrupt (INT) output.

| Signal Name           | SoC Pin |

|-----------------------|---------|

| LPD_MIO25_GEM0_MDIO   | Y9      |

| LPD_MIO24_GEM0_MDC    | Y8      |

| LPD_MIO11_GEM0_RX_CTL | Y3      |

| LPD_MIO10_GEM0_RXD3   | V3      |

| LPD_MIO9_GEM0_RXD2    | U3      |

| LPD_MIO8_GEM0_RXD1    | T3      |

| LPD_MIO7_GEM0_RXD0    | U2      |

| LPD_MIO6_GEM0_RX_CLK  | V2      |

| LPD_MIO5_GEM0_TX_CTL  | W2      |

| LPD_MIO4_GEM0_TXD3    | Y2      |

| LPD_MIO3_GEM0_TXD2    | Y1      |

| LPD_MIO2_GEM0_TXD1    | W1      |

| LPD_MIO1_GEM0_TXD0    | U1      |

| LPD_MIO0_GEM0_TX_CLK  | T1      |

| P1_GEM0_RST_B         | N/C     |

**Table 7 – Ethernet RGMII Pin Assignments**

# 6 VE2302 SOM External Resources

The VE2302 SOM provides sufficient resources to end-user carrier cards to implement fully customized systems that meet their application requirements. The VE2302 SOM provides the following external interfaces to end-user carrier cards (signal directions are with respect to the VE2302 SOM) via three JX Micro Headers.:

- 80 User XPIO Pins

- 22 User HDIO Pins

- 12 User LPD MIO Pins

- 13 User PMC MIO Pins

- 8 GTYP Transceivers

- 4 GTYP Reference Clock Inputs

- System Reference Clock Inputs

- USB 2.0 Connector Interface

- Gigabit Ethernet RJ45 Jack Interface

- PMBus Interface

- Carrier Card I2C Interface

- SOM Boot Mode Interface

- SOM JTAG Interface

- SOM SYSMON interface

- SOM Reset Input

- SOM Status Signals

- Carrier Card Interrupt Input

- Carrier Card Reset Output

- SOM Input Voltages and Output Sense Pins

- Power Sequencing Control Signals

- SOM Power Good Output

- SOM Battery Input

The following tables summarize connections to the VE2302 SOM JX Micro Header Connectors to external interfaces.

|           | Micro Header JX1                                                    |              |      |

|-----------|---------------------------------------------------------------------|--------------|------|

| Interface | Signal Name                                                         | Source       | Pins |

| PMC       | Bank 502 PMC MIO                                                    | Bank 502     | 12   |

|           | Bank 501 PMC MIO                                                    | Bank 501     | 13   |

|           | JTAG_TMS, JTAG_TCK, JTAG_TDI, JTAG_TDO ERROR_OUT DONE_OUT MODE[0:3] | Bank 503     | 10   |

| PL I/O    | Bank 302 Differential Pair I/Os                                     | Bank 302     | 22   |

|           | SYSCLK_P/N                                                          | Bank 702     | 2    |

| Comms     | I2C_P6_GPIO, I2C_P7_GPIO                                            | I2C Expander | 2    |

|           | USB2.0 PHY Interface                                                | USB PHY      | 4    |

|           | Gigabit Ethernet PHY Interface                                      | ETH PHY      | 10   |

| SYSMON    | SMON_V_P, SMON_V_N<br>SMON_VREF<br>VCCAUX_SMON<br>GND_SMON          | Bank 500     | 8    |

| Control   | PMBus                                                               | I2C Switch   | 3    |

|           | CC I2C BUS                                                          | I2C Switch   | 3    |

|           | SOM_PG_OUT                                                          | VE2302 SOM   | 1    |

| Power     | GND                                                                 |              | 39   |

|           | +VCC_BATT                                                           |              | 1    |

|           | +VCC_FUSE                                                           | Carrier Card | 1    |

|           | +VCC_RAM and VCC_RAM_SENSE                                          |              | 2    |

|           | +VCCO_302 and VCCO_302_SENSE                                        |              | 3    |

|           | +VCCO_502                                                           | VE2302 SOM   | 1    |

|           | +VCCO_PMC_MIO                                                       | VE2302 SOM   | 1    |

|           | VCCINT_SENSE and GND_SENSE                                          | VE2302 SOM   | 2    |

|           | +VCCINT                                                             | Carrier Card | 20   |

Table 8 - Micro Header JX1 Summary

|           | Micro Header JX2                                                                    |              |      |

|-----------|-------------------------------------------------------------------------------------|--------------|------|

| Interface | Signal Name                                                                         | Source       | Pins |

| PL        | Bank 702 Differential Pair I/Os                                                     | Bank 702     | 28   |

|           | Bank 702 – DDRMC Do Not Connect                                                     | Bank 702     | 24   |

|           | Bank 703 Differential Pair I/Os                                                     | Bank 703     | 52   |

| Control   | SOM_RESET_IN_B, SOM_PWR_ENB_IN, VCCO_702_PG_IN                                      | Carrier Card | 3    |

|           | VCCO_702_ENB_OUT, CC_RESET_OUT_B                                                    | VE2302 SOM   | 2    |

| Power     | GND                                                                                 |              | 28   |

|           | +VCCO_702                                                                           |              | 2    |

|           | +VCCO_703                                                                           | Carrier Card | 2    |

|           | +MGTYPAVCC                                                                          |              | 3    |

|           | +MGTYPVCCAUX                                                                        |              | 2    |

|           | +VCCAUX_PMC                                                                         |              | 1    |

|           | VCCO_702_SENSE, VCCO_702_SENSE, MGTYPVCCAUX_SENSE, MGTYPAVCC_SENSE, MGTYPAVTT_SENSE | VE2302 SOM   | 5    |

|           | +VCCINT                                                                             | Carrier Card | 8    |

Table 9 - Micro Header JX2 Summary

| Micro Header JX3 |                                 |                |      |  |

|------------------|---------------------------------|----------------|------|--|

| Interface        | Signal Name                     | Source         | Pins |  |

| GTYP             | Bank 103 Differential Pair I/Os | Bank 103       | 20   |  |

|                  | Bank 104 Differential Pair I/Os | Bank 104       | 20   |  |

| Power            | GND                             | On all a Const | 92   |  |

|                  | +MGTYPAVTT                      | Carrier Card 3 |      |  |

|                  | VIN_SENSE                       | VE2302 SOM     | 1    |  |

|                  | +VIN                            | Camian Cand    | 12   |  |

|                  | +VCCINT                         | Carrier Card   | 12   |  |

Table 10 - Micro Header JX3 Summary

The following table shows the VE2302 SOM external interfaces with a brief description of each interface.

| Signal Name                                                                                                                                                           | # of<br>Pins | Description                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPD_MIO[12:23]                                                                                                                                                        | 12           | LPD MIO Interface – 12 LPD MIO pins from bank 502.                                                                                                                                                                                                                        |

| PMC_MIO[37:49]                                                                                                                                                        | 13           | PMC MIO Interface – 13 PMC MIO pins from bank 501.                                                                                                                                                                                                                        |

| USB_D_P,<br>USB_D_N,<br>USB_ID,<br>USB_VBUS,                                                                                                                          | 4            | USB 2.0 PHY Interface – These pins are used by end-user carrier cards to implement a USB 2.0 interface. Please refer to the USB3321 datasheet for AC and DC spec of these signals.                                                                                        |

| ETH_MD[1:4]_P,<br>ETH_MD[1:4]_N,<br>ETH_ACT,<br>ETH_LINK,                                                                                                             | 10           | Gigabit Ethernet PHY Interface – These pins are used by end-user carrier cards to implement a Gigabit Ethernet interface. Please refer to the KSZ9131 datasheet for AC and DC spec of these signals.                                                                      |

| GTYP_10[3:4]_TX[0:3]_P,<br>GTYP_10[3:4]_TX[0:3]_N,<br>GTYP_10[3:4]_RX[0:3]_P,<br>GTYP_10[3:4]_RX[0:3]_N,<br>GTYP_10[3:4]_REFCLK[0:1]_P,<br>GTYP_10[3:4]_REFCLK[0:1]_N | 40           | GTYP Transceivers Interface – The transceiver data and clock signals are used by the end-user carrier cards to implement various multi-gigabit interfaces. Please refer to the Xilinx DS958 (Versal AI Edge SoC DataSheet) datasheet for AC and DC spec of these signals. |

| CC_SDA, CC_SCL, CC_INT_B                                                                                                                                              | 3            | Carrier Card I2C Interface – This I2C interface will be used to interface to end-user carrier cards I2C slave devices.                                                                                                                                                    |

| XPIO_702_*<br>XPIO_703_*                                                                                                                                              | 80           | XPIO User Interfaces – These pins are connected to the PL banks 702 and 703. These signals can be used by end-user carrier cards as single-ended or differential pairs. Please refer to the Xilinx AM010 and DS958 for more information on the XPIOs.                     |

| HDIO_302_*                                                                                                                                                            | 22           | HDIO – These pins are connected to the HDIO bank 302.  These signals can be used by end-user carrier cards as single-ended or differential pairs. Please refer to the Xilinx AM010 and DS958 for more information on the HDIOs.                                           |

| JTAG_TMS, JTAG_TCK, JTAG_TDI, JTAG_TDO                                                                                                                                | 4            | JTAG Interface – These pins are used to interface to the APSoC JTAG port and driven by a JTAG cable on end-user carrier cards.                                                                                                                                            |

| SMON_V_P, SMON_V_N, SMON_VREF, VCCAUX_SMON, SMON_AGND (x4)                                                                                                            | 8            | SYSMON Interface – End-user carrier cards can use these pins to drive low speed analog signals into the System Monitor interface. Please refer to the Xilinx AM006 and DS958 for more information on the System Monitor interface.                                        |

| PMBUS_DATA, PMBUS_CLK, PMBUS_ALERT_B                                                                                                                                  | 3            | PMBus Interface – This PMBus interface is used to program and/or monitor the PMBus voltage regulators on end-user carrier cards (optional).                                                                                                                               |

| I2C_P6_GPIO,<br>I2C_P7_GPIO                                                                                                                                           | 2            | I2C Expander GPIO – These pins are connected to the I2C 8-Bit IO Expander. These signals can be used end-user carrier cards as single-ended input or output signals.                                                                                                      |

| MODE[0:3]                                                                                                                                                             | 4            | <b>Boot Mode Signals</b> – These signals are used to select the primary boot device.                                                                                                                                                                                      |

| SYSCLK_P,<br>SYSCLK_N                                                                                                                                                 | 2            | <b>System Reference Clock</b> – 200MHz LVDS oscillator sourced by the end-user carrier card and used by LPDDR4 interface.                                                                                                                                                 |

| ERROR_OUT                                                                                                                                              | 1  | Bank 503 Error Signal – 1.8V sourced by the SOM indicating                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DONE_OUT                                                                                                                                               | 1  | a boot error occurred.  Bank 504 Done Signal – 1.8V sourced by the SOM indicating                                                                                                                                                                                  |

| SOM_RESET_IN_B, CC_RESET_OUT_B                                                                                                                         | 2  | configuration complete.  Reset Signals – These reset signals are used to reset the SOM or the devices on end-user carrier cards.                                                                                                                                   |

| +VCCO_302                                                                                                                                              | 2  | Bank 302 VCCO – 1.8 to 3.3V sourced by the end-user carrier cards dependent on interface implementation.                                                                                                                                                           |

| +VCCO_702                                                                                                                                              | 2  | Bank 702 VCCO – 1.0 to 1.5V sourced by the end-user carrier card dependent on interface implementation.                                                                                                                                                            |

| +VCCO_703                                                                                                                                              | 2  | <b>Bank 703 VCCO</b> – 1.0 to 1.5V sourced by the end-user carrier card dependent on interface implementation.                                                                                                                                                     |

| +MGTYPAVCC                                                                                                                                             | 3  | <b>GTYP Core Voltage</b> – 0.92V sourced by the end-user carrier card if GTYPs are implemented.                                                                                                                                                                    |

| +MGTYPAVTT                                                                                                                                             | 3  | <b>GTYP Termination Voltage</b> – 1.2V sourced by the end-user carrier card if GTYPs are implemented.                                                                                                                                                              |

| +MGTYPVCCAUX                                                                                                                                           | 2  | <b>GTYP Auxiliary Core Voltage</b> – 1.5V sourced by the end-user carrier card if GTYPs are implemented.                                                                                                                                                           |

| +VCCINT                                                                                                                                                | 40 | <b>SOM VCCINT Power</b> – 0.70V (or 0.80V, 0.88V) sourced by the end-user carrier card. Proper regulator sizing is dependent on end-user design implementation. Please reference AMD Power Design Manager (PDM) for proper estimating of needs for this regulator. |

| +VCC_RAM                                                                                                                                               | 1  | <b>SOM RAM VCC</b> – 0.80V (or 0.88V) sourced by the end-user carrier card due to proper sequencing requirements and desire to limit unnecessary handshaking between SOM and carrier card.                                                                         |

| +VCC_BATT                                                                                                                                              | 1  | VBATT Input – 1.5V sourced by the end-user carrier card to support battery backup functionality.                                                                                                                                                                   |

| +VCC_FUSE                                                                                                                                              | 1  | <b>eFUSE Input</b> – 1.8V (or 0V) sourced by the end-user carrier cards to support eFuse functionality.                                                                                                                                                            |

| +VCCO_PMC_MIO                                                                                                                                          | 1  | <b>SOM PMC MIO VCCO</b> – 1.8V sourced by the VE2302 SOM to provide proper reference voltage to carrier card interfaces.                                                                                                                                           |

| +VCCAUX_PMC                                                                                                                                            | 1  | SOM PMC VCCAux – 1.5V sourced by the VE2302 SOM and is used in determination of release point of SOM_RESET_IN_B (POR_B) control signal.                                                                                                                            |

| +VCCO_502                                                                                                                                              | 1  | Bank 502 VCCO – 1.8V sourced by the VE2302 SOM to provide proper reference voltage to carrier card interfaces.                                                                                                                                                     |

| MGTYPAVCC_SENSE, MGTYPAVTT_SENSE, MGTYPVCCAUX_SENSE, VCCO_302_SENSE, VCCO_702_SENSE, VCCO_703_SENSE, VCC_RAM_SENSE, VCCINT_SENSE, VIN_SENSE, GND_SENSE | 10 | Voltage Sense Feedback – These output pins are used by end-user carrier cards to compensate for the voltage loss across the JX connectors by providing feedback at the termination point of the load.                                                              |

| SOM_PG_OUT | 1   | SOM Power Good Output – This signal is used to enable the end-user carrier card voltage regulators. |

|------------|-----|-----------------------------------------------------------------------------------------------------|

| GND        | 159 | Ground Pins                                                                                         |

| +VIN       | 12  | Main Input Voltage – 5V DC.                                                                         |

Table 11 - VE2302 SOM External Interface Signals

#### 6.1 SYSMON Header

The SYSMON interface is connected to bank 500 of the Versal <sup>™</sup> APSoC and consists of **VP**, **VN**, **VREF**, **VCCAUX** and **AGND** pins. These pins are routed to the **JX1** connector and can be used on end-user carrier cards to implement low speed analog interfaces. The SYSMON supply voltages, **VCCAUX** and **VREF** are provided on the VE2302 SOM. If not used, the SYSMON signals can be left unconnected on the end-user carrier card.

The following table shows the VE2302 SOM SYSMON interface pins available on the JX1 connector.

| Signal Name | Signal Name JX1 Pin N |           | Signal Name |

|-------------|-----------------------|-----------|-------------|

| SMON_AGND   | A39 / C39             | B39 / D39 | SMON_AGND   |

| SMON_VREF   | A40                   | B40       | SMON_V_P    |

| SMON_V_N    | C40                   | D40       | VCCAUX_SMON |

Table 12 – SYSMON Interface Pin Assignments

Please refer to the Versal™ Al Edge Carrier Card Hardware User Guide for example implementation details regarding the SYSMON interface to the JX1 connector.

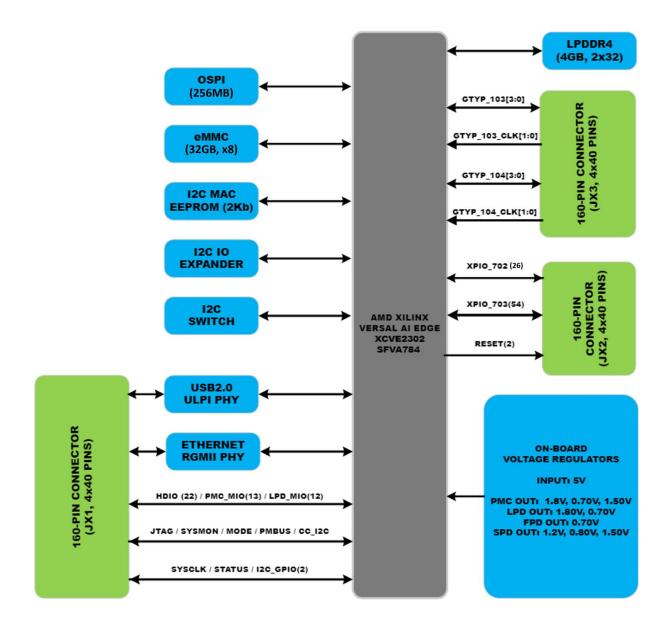

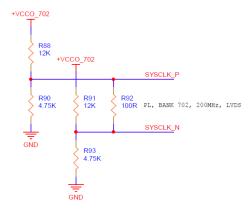

# 6.2 System Clock

The VE2302 SOM requires a differential clock be provided to it from the end-user carrier card to support LPDDR4 implementation. The end-user carrier card shall provide a 200MHz LVDS differential pair to the bank 702 SYSCLK\_P/N differential pins to the JX1 connector.

| JX1 Pin Number | Signal Name | APSoC Pin Number |

|----------------|-------------|------------------|

| D14            | SYSCLK_P    | Bank 702 - N23   |

| D15            | SYSCLK_N    | Bank 702 - N24   |

Table 13 - System Clock Interface Pin Assignments

As an example, the Versal™ AI Edge Carrier Card implements a 200MHz LVDS oscillator:

Figure 2 – Example System Clock Schematic

**NOTE**: The following figure shows the VE2302 SOMs implementation of the termination scheme for the system clock differential pair, **SYSCLK\_P/N**.

Figure 3 – System Clock SOM Termination Schematic

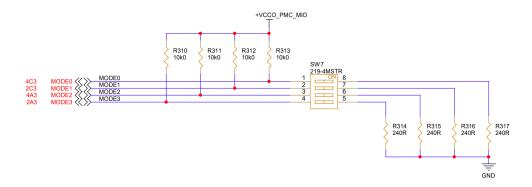

#### 6.3 Boot Mode Interface

The VE2302 SOM routes the boot mode pins to the **JX1** connector. End-user carrier cards should implement a method to control the boot mode pins. An example is provided in the figure below of a small 4-position DIP switch is used to provide control of the boot mode pins. The switch is connected to the **MODE[0:3]** pins of the **JX1** connector and allows users to select the primary boot device.

The MODE[0:3] signals are referenced to +VCCO\_PMC\_MIO voltage rail which is provided on the JX1 connector.

Figure 4 – Example Boot Mode Switch Schematic

| BOOT MODE       | MODE PIN[3:0] | SW7[1-4]      |

|-----------------|---------------|---------------|

| JTAG            | 0x0           | ON-ON-ON      |

| SD0/3.0 AUTODIR | 0x3           | ON-ON-OFF-OFF |

| OSPI            | 0X8           | OFF-ON-ON-ON  |

Table 14 - Supported Boot Modes

| Signal Name | JX1 Pin | Number | Signal Name |

|-------------|---------|--------|-------------|

| MODE0       | A35     | B35    | MODE1       |

| MODE2       | C35     | D35    | MODE3       |

**Table 15 – Boot Mode Interface Pin Assignments**

#### 6.4 JTAG Interface

The VE2302 SOM routes the JTAG interface to the **JX1** connector. End-user carrier card must provide the JTAG to the VE2302 SOM to ensure debug and programming capability. The JTAG interface pull-ups and series termination resistors will exist on the end-use carrier card. The JTAG TCK line has an RC (two-footprints) routed on the VE2302 SOM near the Versal<sup>™</sup> AI Edge device.

End-user carrier cards can implement the JTAG interface using JTAG header interfaces such as the Xilinx PC4 header, a USB-JTAG module such as the Digilent SMT2 module or designing the JTAG interface using chip-down methods such as with an FTDI device.

The JTAG interface on end-user carrier cards must drive the JTAG interface on the **JX1** connector with 1.8V IO signaling. The following table shows the VE2302 SOM JTAG interface pins available on the JX1 connector.

The JTAG interface signals are referenced to **+VCCO\_PMC\_MIO** voltage rail which is provided on the **JX1** connector.

| Signal Name | JX1 Pin | Number | Signal Name |

|-------------|---------|--------|-------------|

| JTAG_TCK    | A37     | B37    | JTAG_TMS    |

| JTAG_TDI    | C37     | D37    | JTAG_TDO    |

Table 16 – JTAG Interface Pin Assignments

Please refer to the **Versal™ AI Edge Carrier Card Hardware User Guide** for an example implementation of a USB JTAG-UART with a PC4 header tied to the VE2302 SOM JTAG interface.

# 6.5 Status Signals

The VE2302 SOM routes two status signals to the **JX1** connector. End-user carrier card should implement a method to monitor and/or respond to status signals. The **two status** signals are referenced to **+VCCO\_PMC\_MIO** voltage rail which is provided on the **JX1** connector.

As an example, the Versal<sup>™</sup> Al Edge Carrier Card implements a Blue Diffused 2SMD LED (**D36**) indicating the configuration complete. The **DONE\_OUT** signal is a 1.8V signal and care must be taken to ensure that the LED illuminates properly.

Figure 5 - DONE\_OUT LED Schematic

| I/O Net Name | JX Connector |

|--------------|--------------|

| DONE_OUT     | JX1-D28      |

Table 17 - DONE\_OUT LED Pin Assignment

Similarly, as an example, the Versal<sup>™</sup> Al Edge Carrier Card implements an **ERROR\_OUT** Red Diffused 2SMD LED (**D37**). The **ERROR\_OUT** signal is a 1.8V signal and care must be taken to ensure that the LED illuminates properly.

Figure 6 - ERROR\_OUT LED Schematic

| I/O Net Name | JX Connector |

|--------------|--------------|

| ERROR_OUT    | JX1-D13      |

Table 18 - ERROR\_OUT LED Pin Assignment

#### 6.6 Power-On Reset

The Power-On Reset (POR\_B) circuit for the AMD Versal™ AI Edge device is required to be implemented

on the end-user carrier card. The **POR\_B** is an active-low input signal to the AMD Versal<sup>™</sup> Al Edge device that acts as a master reset. The signal name associated with **POR\_B** port on the AMD Versal<sup>™</sup> Al Edge device is **SOM\_RESET\_IN\_B** and that signal is provided on the **JX2** connector (**Pin JX2-B32**). The VE2302 SOM does provided a 10K-ohm pull-up to **+VCCO\_PMC\_MIO** (1.8V) on **SOM\_RESET\_IN\_B**. The **SOM\_RESET\_IN\_B** signal is referenced to **+VCCO\_PMC\_MIO** voltage rail which is provided on the **JX1** connector.

Please refer to the Versal™ Al Edge Carrier Card Hardware User Guide for an example implementation of SOM\_RESET\_IN\_B control.

The external reset, SOM\_RESET\_IN\_B, can reset the end-user carrier card thru an open-drain signal on the JX2 connector, CC\_RESET\_OUT\_B. The VE2302 SOM is also capable of issuing a soft reset to the end-user carrier card by asserting Port 5 of the I2C I/O Expander, P5\_CC\_RST\_B, using the VE2302 SOM two-wire serial interface. This will soft reset the end-user carrier card thru the same open-drain signal on the JX2 connector (Pin JX2-C14), CC\_RESET\_OUT\_B.

NOTE: Gate U16 re[resents a logic NAND function.

Figure 7 – Carrier Card Output Reset Circuit

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding Port 5 of the I2C 8-bit IO Expander a soft reset for end-user carrier cards.

Please refer to the Versal™ Al Edge Carrier Card Hardware User Guide for an example implementation of CC RESET OUT B control.

| Control Signal Name | JX2 Connector | Voltage            | Active-State |

|---------------------|---------------|--------------------|--------------|

| SOM_RESET_IN_B      | JX2-B32       | +1.8V (SOM)        | Low          |

| CC_RESET_OUT_B      | JX2-C14       | Open-Drain to User | Low          |

Table 19 – Power-On Reset Pin Assignments

#### 6.7 Carrier Card I2C Interface

The VE2302 SOM provides an isolated I2C bus (CC\_SDA, CC\_SCL, and CC\_INT\_B) to the end-user carrier cards via an on-board I2C switch. The carrier card I2C interface is provided to the end-user carrier card via the JX1 connector so that software can communicate with slave I2C devices that reside on the end-user carrier card with little concern to I2C address overlap with slave I2C devices that exist on the VE2302 SOM.

The carrier card I2C interface is connected to channel 0 of the I2C 2-channel switch device on the VE2302 SOM. End-user carrier cards can drive the **INT0** of the channel 0 via **CC\_INT\_B** if desired. The **CC\_INT\_B** (an active low signal) is not specific to the I2C interface and can be used as a general-purpose interrupt from end-user carrier cards to the VE2302 SOM. If not used, the **CC\_INT\_B** signal must be pulled up to 1.8V, 2.5V, or 3.3V on the carrier card.

There are no I2C pullups implemented on carrier card I2C interface on the VE2302 SOM. This allows the end-user carrier card designer to tailor the I2C implementation toward the I2C bus needs on that board.

| Signal Name | JX1 Pin Number |     | Signal Name |

|-------------|----------------|-----|-------------|

| CC_INT_B    | A25            | B25 | CC_SCL      |

| CC_SDA      | C29            |     |             |

## Table 20 - Carrier Card I2C Interface Pin Assignments

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the 2-Channel I2C Switch.

#### 6.8 PMBus Interface

The VE2302 SOM provides an isolated I2C bus (PMBUS\_SDA, PMBUS\_SCL, and PMBUS\_ALERT\_B) to the end-user carrier cards via an on-board I2C switch. The carrier card PMBus interface is provided to the end-user carrier card via the JX1 connector so that software can communicate with slave PMBuS / I2C devices that reside on the end-user carrier card with little concern to I2C address overlap with slave I2C devices that exist on the VE2302 SOM.

The carrier card PMBus interface is connected to channel 1 of the I2C 2-channel switch device on the VE2302 SOM. End-user carrier cards can drive the **INT1** of the channel 0 via **PMBUS\_ALERT\_B** if desired. The **PMBUS\_ALERT\_B** (an active low signal) is not specific to the I2C interface and can be used as a general-purpose interrupt from end-user carrier cards to the VE2302 SOM. If not used, the **PMBUS\_ALERT\_B** signal must be pulled up to 1.8V, 2.5V, or 3.3V on the carrier card.

For PMBus based voltage regulators, after initial programming of the regulators, the VE2302 SOM can utilize the PMBus (via channel 1 of the I2C switch) to control/monitor the PMBus voltage regulators for the purpose of power management and/or monitoring.

There are no PMBus pullups implemented on carrier card PMBus interface on the VE2302 SOM. This allows the end-user carrier card designer to tailor the PMBus implementation toward the PMBus needs on that board.

| Signal Name   | JX1 Pin Number |     | Signal Name |

|---------------|----------------|-----|-------------|

| PMBUS_ALERT_B | A26            | B28 | PMBUS_SDA   |

| PMBUS_SCL     | C30            |     |             |

## Table 21 - PMBus Interface Pin Assignments

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the 2-Channel I2C Switch.

Please refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** for example implementation details regarding the PMBus, PMBus programming header, and a PMBus based voltage regulator.

## 6.9 I2C GPIO Expander Ports

The I2C 8-bit IO expander on the VE2302 SOM provides 2 GP (General Purpose) IO pins for use on enduser carrier cards. These I2C driven general purpose pins are routed to the **JX1** connector and can be used to implement any interface that does not demand high performance. These GPIO ports are open-drain and require pull-ups be implemented on the end-user carrier card.

Please refer to the **FXL6408UMX** device datasheet for the supported voltages on the GPIO ports of the I2C 8-bit IO expander.

The following table shows the end-user carrier card I2C 8-bit expander pins available on the **JX1** connector.

| Signal Name | JX1 Pin Number |

|-------------|----------------|

| I2C_P6_GPIO | C18            |

| I2C_P7_GPIO | C19            |

**Table 22 – IO Expander GPIO PIN Assignments**

Please refer to the **VE2302 SOM Hardware User Guide** for implementation details regarding the I2C 8-bit Expander.

Please refer to the **VE2302 SOM Hardware User Guide** for an example implementation regarding the two available I2C GPIO Expander ports.

#### 6.10 USB2.0 Connector

The physical USB connector is not populated on the VE2302 SOM. The SOM is designed to have the physical USB connector reside on the end-user carrier card. The three USB connector signals (**USB\_D\_P**, **USB\_D\_N** and **USB\_ID**) and **+USB\_VBUS** are connected to the **JX1** Micro Header. The table below shows the connections of these signals at JX1.

| Signal Name | JX1 Pin |

|-------------|---------|

| USB_D_P     | D29     |

| USB_D_N     | D30     |

| USB_ID      | B30     |

| +USB_VBUS   | D12     |

Table 23 - USB2.0 PHY JX1 Pin Assignments

Please refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** for example implementation details regarding the USB2.0 Type-A Connector.

#### 6.11 RJ45 GbE Jack

The physical RJ45 GbE jack and magnetics are not populated on the VE2302 SOM. The VE2302 SOM is designed to have the physical RJ45 GbE jack and magnetics reside on the end-user carrier card. The RJ45 GbE jack connector signals are connected to the **JX1** Micro Header.

| Signal Name | JX1 Pin |

|-------------|---------|

| ETH_MD1_P   | D32     |

| ETH_MD1_N   | D33     |

| ETH_MD2_P   | C32     |

| ETH_MD2_N   | C33     |

| ETH_MD3_P   | B32     |

| ETH_MD3_N   | B33     |

| ETH_MD4_P   | A32     |

| ETH_MD4_N   | A33     |

| ETH_ACT     | A29     |

| ETH_LINK    | A30     |

Table 24 - Ethernet PHY JX1 Pin Assignments

Please refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** for example implementation details regarding the RJ45 GbE jack.

#### 6.12 PMC MIO Interfaces

The PMC MIO interface consists of 13 PMC MIO pins (**PMC\_MIO[37:49]**) connected to the PMC MIO bank 501. These MIO pins are routed to the **JX1** connector and are available for processor interface implementation on end-user carrier cards. These PMC MIO banks are operated at 1.8V and are referenced to **+VCCO\_PMC\_MIO** voltage.

On the Versal™ AI Edge Carrier Card, PMC MIO pins are used to implement the following interfaces:

- microSD

- Push Buttons x2

- LEDs x2

Please refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** for example implementation details regarding the physical interfaces mapped to the LPD MIO pins.

| Signal Name | JX1 Pin Number |     | Signal Name |

|-------------|----------------|-----|-------------|

| PMC_MIO49   | B19            | B23 | PMC_MIO42   |

| PMC_MIO48   | B20            | C26 | PMC_MIO41   |

| PMC_MIO47   | A19            | C27 | PMC_MIO40   |

| PMC_MIO46   | A20            | D23 | PMC_MIO39   |

| PMC_MIO45   | A22            | D24 | PMC_MIO38   |

| PMC_MIO44   | A23            | D26 | PMC_MIO37   |

| PMC_MIO43   | B22            | -   | -           |

Table 25 – PMC MIO Pin Assignments

Please review the Versal<sup>™</sup> Adaptive SoC Technical Reference Manual (**AM011**) for interfaces that can be mapped to the 13 available PMC MIO pins.

#### 6.13 LPD MIO Interfaces

The LPD MIO interface consists of 12 LPD MIO pins (LPD\_MIO[12:32]) connected to the LPD MIO bank 502. These MIO pins are routed to the JX1 connector and are available for processor interface implementation on end-user carrier cards. These LPD MIO banks are operated at 1.8V and are referenced to +VCCO\_PMC\_MIO voltage.

On the Versal™ AI Edge Carrier Card, LPD MIO pins are used to implement the following interfaces:

- CAN Interfaces x2

- I2C Interface

- UART

Please refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** for example implementation details regarding the physical interfaces mapped to the LPD MIO pins.

| Signal Name | JX1 Pin Number |     | Signal Name |

|-------------|----------------|-----|-------------|

| LPD_MIO23   | A16            | D17 | LPD_MIO17   |

| LPD_MIO22   | A17            | D18 | LPD_MIO16   |

| LPD_MIO21   | B16            | D20 | LPD_MIO15   |

| LPD_MIO20   | B17            | D21 | LPD_MIO14   |

| LPD_MIO19   | C21            | C23 | LPD_MIO13   |

| LPD_MIO18   | C22            | C24 | LPD_MIO12   |

**Table 26 – LPD MIO Pin Assignments**

Please review the Versal<sup>™</sup> Adaptive SoC Technical Reference Manual (**AM011**) for interfaces that can be mapped to the 12 available LPD MIO pins.

#### 6.14 HDIO Interfaces

The HDIO interface consists of 22 HD (High Density) IO pins (HDIO\_302\_L[0:10]\_P/N]) connected to VE2302 SOM via the HDIO bank 302. These HDIO pins are routed to the JX1 connector and are available for programmable interface implementation on end-user carrier cards. The HDIO banks is operated at between 1.8V and 3.3V and are referenced to +VCCO\_302 voltage from the end-user carrier card via the JX1 connector.

On the Versal™ AI Edge Carrier Card, the HDIO pins are used to implement the following interfaces:

• High-Speed IO (HSIO) Expansion Port

Please refer to the **Versal™ AI Edge Carrier Card Hardware User Guide** for example implementation details regarding the HSIO Expansion Port mapping to the HDIO pins as well as how **+VCCO\_302** provide +1.8V or +3.3V onto that voltage rail for bank 302.

| Signal Name        | JX1 Pin Number |     | Signal Name   |

|--------------------|----------------|-----|---------------|

| HDIO_302_L10_P     | A7             | D10 | HDIO_302_L4_P |

| HDIO_302_L10_N     | A8             | D11 | HDIO_302_L4_N |

| HDIO_302_L9_P      | B7             | A13 | HDIO_302_L3_P |

| HDIO_302_L9_N      | B8             | A14 | HDIO_302_L3_N |

| HDIO_302_L8_P      | C7             | B10 | HDIO_302_L2_P |

| HDIO_302_L8_N      | C8             | B11 | HDIO_302_L2_N |

| HDIO_302_L7_P      | D7             | A10 | HDIO_302_L1_P |

| HDIO_302_L7_N      | D8             | A11 | HDIO_302_L1_N |

| HDIO_302_HDGC_L6_P | C10            | C13 | HDIO_302_L0_P |

| HDIO_302_HDGC_L6_N | C11            | C14 | HDIO_302_L0_N |

| HDIO_302_HDGC_L5_P | B13            | -   | -             |

| HDIO_302_HDGC_L5_N | B14            | -   | -             |

Table 27 – HDIO Pin Assignments

#### 6.15 XPIO Interfaces

The XPIO interface consists of 54 XP (Extended Performance) IO pins from bank 703 (XPIO\_703\_L[0:26]\_P/N]) and 26 XP (Extended Performance) IO pins from bank 702 (XPIO\_702\_L[\*]\_P/N) connected to VE2302 SOM. These XPIO pins are routed to the JX2 connector and are available for programmable interface implementation on end-user carrier cards. The XPIO banks are operated at between 1.1V and 1.5V and are referenced to +VCCO\_702 and +VCCO\_703 bank voltages from the end-user carrier card via the JX2 connector.

On the Versal™ AI Edge Carrier Card, the XPIO pins are used to implement the following interfaces:

- MIPI Interfaces x4

- HDMI Control Signals

- SFP28 Control Signals

Please refer to the **Versal™ Al Edge Carrier Card Hardware User Guide** for example implementation details regarding bank 702 and bank 703 mapping of the XPIO pins to physical interfaces.

**NOTE**: XPIO Bank 702 contains four signals mapped to the PIN EFFICIENT LPDDR4 interface. These four signals are associated to a bank voltage of +1.1V which creates a potential for a mismatch with the bank voltage desired to be utilized on bank 702 by an end-user carrier card, such as a bank voltage like 1.2V or 1.5V. A workaround for this exists and is documented in **AMD Answer Record 35358** which helps to resolve voltage standard conflicts for pin efficient topologies.

NOTE: Link to Answer Record 35358: <u>Versal™ Adaptive SOC DDRMC - Change LPDDR4 RESET\_N</u> and SYS\_CLK IO Standards for Pin Efficient Topologies

| Signal Name           | JX2 Pin | Number | Signal Name           |

|-----------------------|---------|--------|-----------------------|

| XPIO_703_L26_P        | C12     | C21    | XPIO_703_GC_XCC_L12_P |

| XPIO_703_L26_N        | C13     | C22    | XPIO_703_GC_XCC_L12_N |

| XPIO_703_L25_P        | D12     | A6     | XPIO_703_L11_P        |

| XPIO_703_L25_N        | D13     | A7     | XPIO_703_L11_N        |

| XPIO_703_GC_XCC_L24_P | C9      | А3     | XPIO_703_L10_P        |

| XPIO_703_GC_XCC_L24_N | C10     | A4     | XPIO_703_L10_N        |

| XPIO_703_L23_P        | B18     | B6     | XPIO_703_GC_XCC_L9_P  |

| XPIO_703_L23_N        | B19     | B7     | XPIO_703_GC_XCC_L9_N  |

| XPIO_703_L22_P        | B16     | D15    | XPIO_703_L8_P         |

| XPIO_703_L22_N        | B16     | D16    | XPIO_703_L8_N         |

| XPIO_703_XCC_L21_P    | A15     | C15    | XPIO_703_L7_P         |

| XPIO_703_XCC_L21_N    | A16     | C16    | XPIO_703_L7_N         |

| XPIO_703_L20_P        | A18     | D18    | XPIO_703_GC_XCC_L6_P  |

| XPIO_702_L20_N        | A19     | D19    | XPIO_703_GC_XCC_L6_N  |

| XPIO_703_L19_P        | B21     | D3     | XPIO_703_L5_P         |

| XPIO_703_L19_N        | B22     | D4     | XPIO_703_L5_N         |

| XPIO_703_XCC_L18_P    | A21     | C3     | XPIO_703_L4_P         |

| XPIO_703_XCC_L18_N    | A22     | C4     | XPIO_703_L4_N         |

| XPIO_703_L17_P        | B12     | В3     | XPIO_703_XCC_L3_P     |

| XPIO_703_L17_N        | B13     | B4     | XPIO_703_XCC_L3_N     |

| XPIO_703_L16_P        | A9      | D6     | XPIO_703_L2_P         |

| XPIO_703_L16_N        | A10     | D7     | XPIO_703_L2_N         |

| XPIO_703_XCC_L15_P    | A12     | C6     | XPIO_703_L1_P         |

| XPIO_703_XCC_L15_N    | A13     | C7     | XPIO_703_L1_N         |

| XPIO_703_L14_P        | C18     | D9     | XPIO_703_XCC_L0_P     |

| XPIO_703_L14_N        | C19     | D10    | XPIO_703_XCC_L0_N     |

| XPIO_703_L13_P        | D21     | -      | -                     |

| XPIO_703_L13_N        | D22     | -      | -                     |

Table 28 - XPIO 703 Pin Assignments

| Signal Name        | JX2 Pin Number |     | Signal Name        |

|--------------------|----------------|-----|--------------------|

| XPIO_702_L26_P     | В9             | C30 | XPIO_702_L17_P     |

| XPIO_702_L26_N     | B10            | C31 | XPIO_702_L17_N     |

| XPIO_702_L23_P     | B33            | C27 | XPIO_702_L16_P     |

| XPIO_702_L23_N     | B34            | C28 | XPIO_702_L16_N     |

| XPIO_702_L22_P     | A33            | D30 | XPIO_702_XCC_L15_P |

| XPIO_702_L22_N     | A34            | D31 | XPIO_702_XCC_L15_N |

| XPIO_702_XCC_L21_P | B36            | D39 | XPIO_702_L14_P     |

| XPIO_702_XCC_L21_N | B37            | D40 | XPIO_702_L14_N     |

| XPIO_702_L20_P     | A36            | D36 | XPIO_702_L13_P     |

| XPIO_702_L20_N     | A37            | D37 | XPIO_702_L13_N     |

| XPIO_702_L19_P     | A39            | C39 | XPIO_702_XCC_L12_P |

| XPIO_702_L19_N     | A40            | C40 | XPIO_702_XCC_L12_N |

| XPIO_702_XCC_L18_P | B39            | -   | -                  |

| XPIO_702_XCC_L18_N | B40            | -   | -                  |

Table 29 - XPIO 702 Pin Assignments

#### 6.16 GTYP Interfaces