# PicoZed™ 7010/7020 SOM (System-On-Module) Hardware User Guide

Version 2.0

# **Document Control**

**Document Version:** 2.0

**Document Date:** 03 Feb 2018

## **Prior Version History**

| Version | Date       | Comment                                                                          |

|---------|------------|----------------------------------------------------------------------------------|

| 1.0     | 10/6/2014  | Initial PicoZed 7010/7020 Hardware User Guide                                    |

| 1.1     | 10/30/2014 | DDR3L documented and Diagram Updates                                             |

| 1.2     | 12/2/2014  | Diagram Update Figure 5 and PL IO LVDS support                                   |

| 1.3     | 12/8/2014  | Removed AR numbers for DDR3 and reference UG933                                  |

| 1.4     | 2/3/2015   | Swapper JX3 pin listing in Table 7 for JX3.64/JX3.66                             |

| 1.5     | 12/3/2015  | Updated Figure 3                                                                 |

| 1.6     | 3/11/2016  | Minor document cleanup and incorrect pin listing for PG_MODULE                   |

| 1.7     | 7/6/2016   | Updated Figure 6 with proper TLV62130 part number                                |

| 1.8     | 3/3/2017   | Added detailed Absolute Max, Operating Conditions, and Mechanical specifications |

| 1.9     | 5/4/2017   | Updated Operating Conditions and eMMC pin tables. Minor typographical edits.     |

| 2.0     | 2/3/2018   | Added Rev E changes                                                              |

# Contents

| I | Intr | roduction                                                    | 6  |

|---|------|--------------------------------------------------------------|----|

| 2 | Fui  | nctional Description                                         | 8  |

|   | 2.1  | All Programmable SoC                                         | 8  |

|   | 2.2  | Memory                                                       | 8  |

|   | 2.2. | .1 DDR3L                                                     | 8  |

|   | 2.2. | .2 Quad-SPI Flash                                            | 10 |

|   | 2.2. | .3 eMMC (Multi-Media Controller)                             | 11 |

|   | 2    | 2.2.3.1 Revision C Only                                      | 12 |

|   | S    | Software Control of Multiplexer Select                       | 12 |

|   | F    | Hardware Control of Multiplexer Select (Interface Strapping) | 12 |

|   | 2    | 2.2.3.2 Revision E Only                                      | 14 |

|   | J    | Jumper Option to Enable MIOs on JX2 connector                | 14 |

|   | 2.3  | USB 2.0 OTG                                                  | 15 |

|   | 2.4  | 10/100/1000 Ethernet PHY                                     | 16 |

|   | 2.5  | User I/O                                                     | 18 |

|   | 2.5. | .1 Available PS MIO User Pins                                | 18 |

|   | 2.5. | .2 Available PL IO User Pins                                 | 19 |

|   | 2.6  | Clock Source                                                 | 19 |

|   | 2.7  | Reset Sources                                                | 20 |

|   | 2.7. | .1 Zynq Power-on Reset (PS_POR_B)                            | 20 |

|   | 2.7. | .2 PROGRAM_B, DONE, PUDC_B, INIT_B Pins                      | 20 |

|   | 2.7. | .3 Processor Subsystem Reset                                 | 20 |

|   | 2.8  | Expansion Headers                                            | 21 |

|   | 2.8. | .1 Micro Headers                                             | 21 |

|   | 2.9  | Configuration Modes                                          | 26 |

|   | 2.9. | .1 JTAG Connections                                          | 28 |

|   | 2.10 | Power Supplies                                               | 29 |

|   | 2.10 | • •                                                          |    |

|   | 2.10 | 0.2 Voltage Regulators                                       | 30 |

|   | 2.10 | 0.3 Power Supply Sequencing                                  | 32 |

|   | 2.10 | 0.4 PCB Bypass / Decoupling Strategy                         | 34 |

|   | 2.10 | 0.5 Power Good LED                                           | 34 |

|   | 2.10 | 0.6 Power Estimation                                         | 34 |

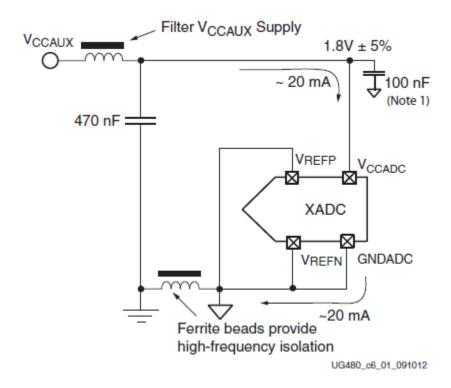

|   | 2.10 | 0.7 XADC Power Configuration                                 | 35 |

|   | 2.10 | 0.8 Battery Backup - Device Secure Boot Encryption Key       | 35 |

|   | 2.10 | 0.9 Thermal Mitigation                                       | 36 |

| 3  | Zyn                          | q-7000 AP SoC I/O Bank Allocation                                   | . 37 |

|----|------------------------------|---------------------------------------------------------------------|------|

|    | 3.1                          | PS MIO Allocation                                                   | . 37 |

|    | 3.2                          | Zynq-7000 AP SoC Bank Voltages                                      | . 38 |

| 4  | Spe                          | cifications and Ratings                                             | . 39 |

|    | 4.1                          | Absolute Maximum Ratings                                            | . 39 |

|    | 4.2                          | Recommended Operating Conditions                                    | . 41 |

|    | 4.3                          | Mechanical                                                          | . 43 |

|    | 4.3.                         | •                                                                   |      |

|    | 4.3.2                        | 3                                                                   |      |

|    | 4.3.3                        |                                                                     |      |

|    | 4.3.4                        |                                                                     |      |

| _  | 4.3.                         | •                                                                   |      |

| 5  | Dis                          | claimer                                                             | . 45 |

|    | <b>igur</b><br>gure <i>1</i> | es  - PicoZed Block Diagram                                         | 7    |

|    |                              | 2 – eMMC / JX2 MIO Multiplexer Block Diagram on PicoZed Revision C  |      |

|    |                              | B – Resistor Jumper Option to Choose eMMC or JX2 for MIO Connection |      |

| Fi | gure {                       | 5 – 10/100/1000 Ethernet Interface                                  | . 16 |

|    |                              | 6 – PicoZed 7010/7020 Boot Mode Switch                              |      |

|    |                              | 7 – PicoZed 7010/7020 Power Scheme                                  |      |

| Fi | gure 8                       | B – Regulation Circuitry (VCCIO_EN is PG_1V8)                       | . 30 |

| Fi | gure 9                       | 9 – Power Supply Sequencing                                         | . 32 |

| Fi | gure 1                       | 0 – Power Sequencing with Carrier Card                              | . 33 |

|    |                              | 1 – CLG400 PL Decoupling                                            |      |

| Fi | gure 1                       | 2 – CLG400 PS Decoupling                                            | . 34 |

|    | _                            | 3 – XADC Power Configuration                                        |      |

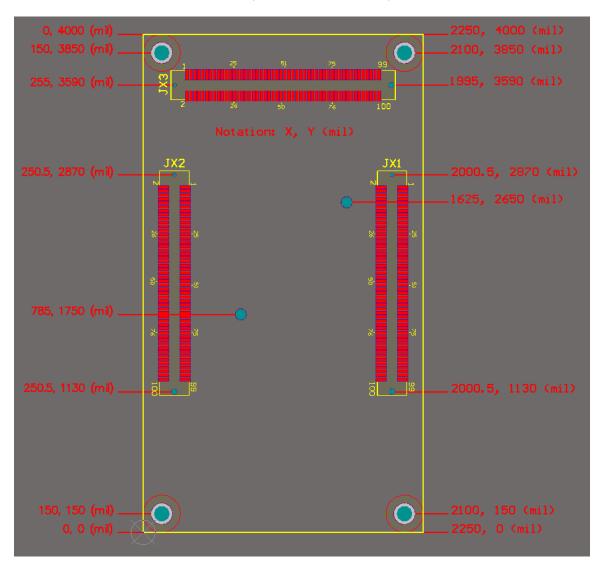

|    |                              | 4 – PicoZed 7010/7020 Top View Mechanical Dimensions                |      |

|    | _                            | 5 – PicoZed 7010/7020 Side View Vertical Dimension                  |      |

|    | _                            | 6 – PicoZed Mounting Hardware                                       |      |

|    | J •                          |                                                                     |      |

# **Tables**

| Table 1 – DDR3L Connections                                     | 9  |

|-----------------------------------------------------------------|----|

| Table 2 – Quad-SPI Flash Pin Assignment and Definitions         | 10 |

| Table 3 – eMMC Pin Assignment and Definitions                   | 11 |

| Table 4 – USB 2.0 JX3 Pin Assignments                           | 15 |

| Table 5 – USB 2.0 Pin Assignment and Definitions                | 16 |

| Table 6 – Ethernet PHY Pin Assignment and Definitions           | 17 |

| Table 7 – PS MIO User Interface                                 | 18 |

| Table 8 – Micro Header JX1 and JX2 Pin Outs                     | 22 |

| Table 9 – Micro Header JX3 Pin Out                              | 22 |

| Table 10 – JX1 Connections                                      | 23 |

| Table 11 – JX2 Connections                                      | 24 |

| Table 12 – JX3 Connections                                      | 25 |

| Table 13 – PicoZed 7010/7020 Configuration Modes                | 27 |

| Table 14 – JTAG Pin Connections                                 | 28 |

| Table 15 – PicoZed 7010/7020 Voltage Rails                      | 30 |

| Table 16 – Voltage Rails w/ Max Output Current                  | 31 |

| Table 17 – PS MIO Interface Requirements                        | 37 |

| Table 18 – PS GPIO Assignments                                  | 37 |

| Table 19 – Zynq Bank Voltage Assignments                        | 38 |

| Table 20 – Absolute Maximum Ambient Temperature Rating          | 39 |

| Table 21 – Absolute Maximum Ratings for Supply Voltages         | 39 |

| Table 22 – Absolute Maximum Ratings for I/O Voltages            | 40 |

| Table 23 – Recommended Ambient Operating Temperature            | 41 |

| Table 24 – Recommended Operating Conditions for Supply Voltages | 41 |

| Table 25 – Recommended Operating Conditions for I/O Voltages    | 42 |

| Table 26 – Mounting Hardware                                    | 44 |

| Table 27 – Mass of SOMs                                         | 44 |

| Table 28 – Mass of Mounting Hardware / Standoffs                | 44 |

| Table 29 – FCI BergStak Connector Ratings                       | 45 |

#### 1 Introduction

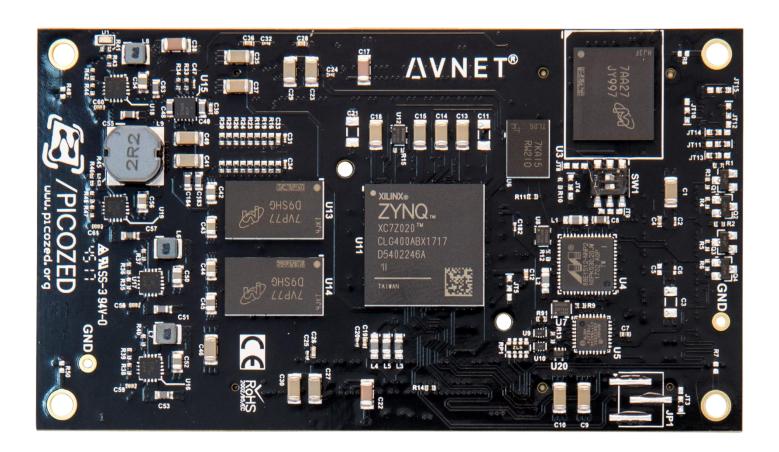

The PicoZed Z7010/Z7020 SOM (System-On Module) is a low cost System-On-Module targeted for broad use in many applications. The features provided by the PicoZed System-On-Module consist of:

- Xilinx XC7Z010-1CLG400 or Xilinx XC7Z020-1CLG400 AP SOC

- Primary configuration = QSPI Flash

- Auxiliary configuration option

- eMMC (Second Stage Bootloader)

- Auxiliary primary configuration options via End User Carrier Card

- JTAG

- microSD Card or SD Card

- Memory

- 1 GB DDR3 (x32)

- 128 Mb QSPI Flash

- eMMC (Revisions C = 4GB; Revision E = 8GB)

- Interfaces

- 10/100/1000 Ethernet PHY (Connector required on End User Carrier Card)

- USB 2.0 OTG PHY (Connector required on End User Carrier Card)

- Three 100-pin Micro Headers

- On-board Oscillator

- 33.333 MHz

- Power

- High-efficiency regulators for VCCINT, VCCPINT, VCCBRAM, VCCAUX, VCCPAUX, VCCPLL, VCCO\_0, VCCO\_DDR, VCCO\_MIO1 and VCCO\_MIO0

- VCCO\_34, VCCO\_35, and VCCO\_13 are powered from Expansion Card via Three 100-pin Micro Headers

- Software

- Vivado Design Suite

- Download from www.xilinx.com/support/download.html

Figure 1 – PicoZed Block Diagram

## **2 Functional Description**

#### 2.1 All Programmable SoC

The PicoZed 7010/7020 includes a Xilinx Zynq XC7Z010-1CLG400 or Zynq XC7Z020-1CLG400 AP SoC. The PicoZed 7010/7020 is available in both commercial and industrial temperature grade options.

#### 2.2 Memory

Zynq contains a hardened PS memory interface unit. The memory interface unit includes a dynamic memory controller and static memory interface modules. PicoZed 7010/7020 takes advantage of these interfaces to provide system RAM as well as two different non-volatile memory sources.

#### 2.2.1 DDR3L

PicoZed 7010/7020 includes two Micron 256M x 16-bit DDR3L memory components creating a 256M x 32-bit interface, totaling 1 GB of random access memory. The DDR3L memory is connected to the hard memory controller in the PS of the Zynq AP SoC. The PS incorporates both the DDR controller and the associated PHY, including its own set of dedicated I/Os.

Speed of up to 1,066 MT/s for DDR3L is supported.

The DDR3L interface is designed to use 1.35V SSTL-compatible inputs by default. There is an option to support 1.5V capable DDR3 devices via a resistor change on the PicoZed 7010/7020. This option is provided as a note on the PicoZed 7010/7020 schematics.

DDR3L Termination is utilized on the PicoZed 7010/7020 and configured for fly-by routing topology. Additionally, the board trace lengths are matched, compensating for the internal package flight times, to meet the requirements listed in the Zynq-7000 AP SoC PCB Design and Pin Planning Guide (UG933).

All single-ended signals are routed with 40 ohm trace impedance. DCI resistors (VRP/VRN), as well as differential clocks, are set to 80 ohms. DDR3-CKE0 is terminated through 40 ohms to VTT. DDR3-ODT has the same 40 ohm to VTT termination. There was a discrepancy in the original Xilinx documentation regarding whether DDR3-RESET# should have 40 ohms to VTT or 4.7K ohm to GND, which is why a resistor jumper circuit was designed in to give both options. Xilinx has since clarified that 4.7K-ohm to GND is the correct configuration for DDR3-RESET#. The default position of the resistor jumper on production units is 1-2 (GND).

Each DDR3L chip has its own 240-ohm pull-down on ZQ. Note DDR-VREF is not the same as DDR-VTT.

| Signal Name    | Description                             | Zynq AP SOC pin   | DDR3 pin         |

|----------------|-----------------------------------------|-------------------|------------------|

| DDR_CK_P       | Differential clock output               | L2                | J7               |

| DDR_CK_N       | Differential clock output               | M2                | K7               |

| DDR_CKE        | Clock enable                            | N3                | K9               |

| DDR_CS_B       | Chip select                             | N1                | L2               |

| DDR_RAS_B      | RAS row address select                  | P4                | J3               |

| DDR_CAS_B      | RAS column address select               | P5                | K3               |

| DDR_WE_B       | Write enable                            | M5                | L3               |

| DDR_BA[2:0]    | Bank address                            | PS_DDR_BA[2:0]    | BA[2:0]          |

| DDR_A[14:0]    | Address                                 | PS_DDR_A[14:0]    | A[14:0]          |

| DDR_ODT        | Output dynamic termination              | N5                | K1               |

| DDR_RESET_B    | Reset                                   | B4                | T2               |

| DDR_DQ[31:0]   | I/O Data                                | PS_DDR_DQ[31:0]   | DDR3_DQ[15:0] x2 |

| DDR_DM[3:0]    | Data mask                               | PS_DDR_DM[3:0]    | LDM/UDM x2       |

| DDR_DQS_P[3:0] | I/O Differential data strobe            | PS_DDR_DQS_P[3:0] | UDQS/LDQS x2     |

| DDR_DQS_N[3:0] | I/O Differential data strobe            | PS_DDR_DQS_N[3:0] | UDQS#/LDQS# x2   |

| DDR_VRP        | I/O Used to calibrate input termination | H5                | N/A              |

| DDR_VRN        | I/O Used to calibrate input termination | G5                | N/A              |

| DDR_VREF[1:0]  | I/O Reference voltage                   | P6 / H6           | VTTREF           |

Table 1 - DDR3L Connections

#### 2.2.2 Quad-SPI Flash

PicoZed 7010/7020 features a 4-bit SPI (quad-SPI) serial NOR flash. Revision C PicoZed is populated with the Spansion S25FL128S (S25FL128SAGBHIA00), while Revision E PicoZed is populated with the Micron MT25QL128 (MT25QL128ABA8E12-0SIT or MT25QL128ABA8E12-1SIT). The Multi-I/O SPI Flash memory is used to provide non-volatile boot, application code, and data storage. It can be used to initialize the PS subsystem as well as configure the PL subsystem (bitstream).

The relevant device attributes are:

- 128Mbit

- Optional densities are available via customization

- x1, x2, and x4 support

- Speeds up to 104 MHz, supporting Zynq configuration rates @ 100 MHz

- In Quad-SPI mode, this translates to 400Mbps

- Powered from 3.3V

The Quad-SPI Flash connects to the Zynq PS QSPI interface. This requires connection to specific pins in MIO Bank 0/500, specifically MIO[1:6,8] as outlined in the Zynq TRM. Quad-SPI feedback mode is used, thus qspi\_sclk\_fb\_out/MIO[8] is connected to a 20K pull-up resistor to 3.3V and nothing else. This allows a QSPI clock frequency greater than FQSPICLK2. The 20K pull-up straps VMODE[1], setting the Bank 1 Voltage to 1.8V.

| Signal Name | Description       | Zynq Pin            | MIO | Quad-SPI Pin |

|-------------|-------------------|---------------------|-----|--------------|

| CS          | Chip Select       | A7 (MIO Bank 0/500) | 1   | C2           |

| DQ0         | Data0             | B8 (MIO Bank 0/500) | 2   | D3           |

| DQ1         | Data1             | D6 (MIO Bank 0/500) | 3   | D2           |

| DQ2         | Data2             | B7 (MIO Bank 0/500) | 4   | C4           |

| DQ3         | Data3             | A6 (MIO Bank 0/500) | 5   | D4           |

| SCK         | Serial Data Clock | A5 (MIO Bank 0/500) | 6   | B2           |

| FB Clock    | QSPI Feedback     | D5 (MIO Bank 0/500) | 8   | N/A          |

Table 2 – Quad-SPI Flash Pin Assignment and Definitions

**Note:** The QSPI data and clock pins are shared with the VMODE set resistors and the BOOT MODE select jumper JT4 and switch SW1.

#### 2.2.3 eMMC (Multi-Media Controller)

PicoZed 7010/7020 features a Micron embedded Multi Media Controller (eMMC) and NAND Flash IC. This is part of Micron's Managed NAND technology. The fully managed eMMC help make technology transitions nearly seamless by handling media management and error correction code (ECC) internally. Managed NAND frees the host controller for increased speed and system performance—and saves significant resources that would otherwise go to hardware and software development.

PicoZed uses the following Micron eMMC components: Revision C: 4GB, v4.41, MTFC4GMDEA-4M IT Revision E: 8GB, v5.0, MTFC8GAKAJCN-4M IT

Additional densities up to 128 GB may be available for custom population and validation. Please speak with your Avnet FAE or email <a href="mailto:customize@avnet.com">customize@avnet.com</a> for more information:

The eMMC is used to provide non-volatile user data storage. The device is NOT capable of being a primary boot device on Zynq-7000, but it is useful as a secondary boot device.

The relevant device attributes are:

- 4GB (Revision C) or 8GB (Revision E)

- Sizes up to 128GB

- Optional densities available via customization

- Industrial temperature range (-40 to +85 C)

- 4-bit data interface

- 52MHz max clock speed

- 50 MHz SDIO high-speed mode operation (Revision E)

- 25MHz standard-speed mode operation (Revision C)

See Xilinx Answer Record #59999: http://www.xilinx.com/support/answers/59999.html

| Signal Name   | Description | Zynq Pin            | MIO | 153-ball<br>eMMC<br>Device Pin** | 169-ball PCB<br>/Schematic<br>Pattern** |

|---------------|-------------|---------------------|-----|----------------------------------|-----------------------------------------|

| EMMC_IO0_4    | Data 0      | E9 (MIO Bank 0/500) | 10  | А3                               | H3                                      |

| EMMC_CMD_4    | Command     | C6 (MIO Bank 0/500) | 11  | M5                               | W5                                      |

| EMMC_CLK_4    | Clock       | D9 (MIO Bank 0/500) | 12  | M6                               | W6                                      |

| CARRIER_SRST# | Reset       | N/A                 | N/A | K5                               | U5                                      |

| EMMC_IO1_4    | Data 1      | E8 (MIO Bank 0/500) | 13  | A4                               | H4                                      |

| EMMC_IO2_4    | Data 2      | C5 (MIO Bank 0/500) | 14  | A5                               | H5                                      |

| EMMC_IO3_4    | Data 3      | C8 (MIO Bank 0/500) | 15  | B2                               | J2                                      |

Table 3 – eMMC Pin Assignment and Definitions

<sup>\*\*</sup> The PicoZed schematic and PCB are labelled and laid out to accommodate eMMC devices with both 153-ball and 169-ball packages. Currently the PicoZed is fabricated with a 153-ball device while the schematic uses the 169-ball pin assignments. Use the table above for cross reference.

#### 2.2.3.1 Revision C Only

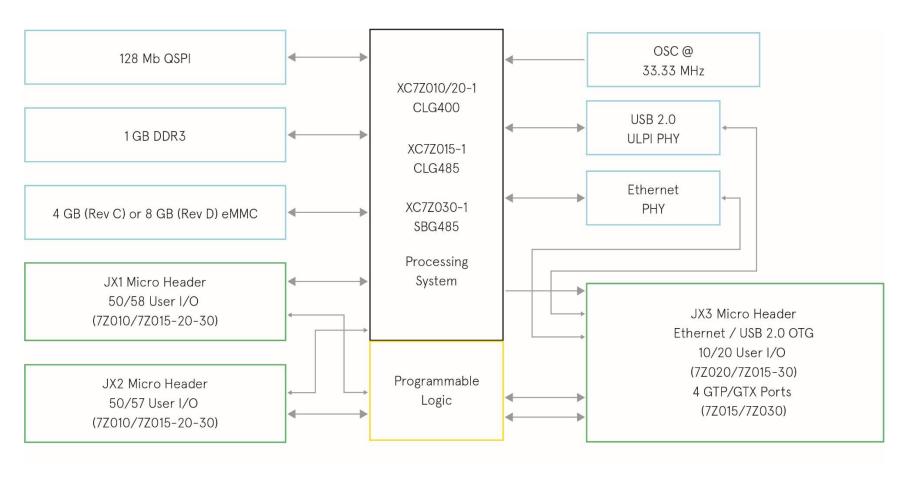

The eMMC connects to the Zynq PS via six MIO signals. On Revision C, these signals are routed through two 4-bit MUXs.

The eMMC I/O is multiplexed with direct connections to the Zynq MIO PS\_MIO[0, 15:9] pins allowing the user to use the JX2 MIO[0, 15:9] pins as standard I/O or have access to the eMMC I/O. The Zynq PS\_MIO0 pin can be used as the multiplexer select control signal to give the user software control to select either interface in real time. Software control and hardware control of the multiplexer select line is discussed in further detail below.

#### Software Control of Multiplexer Select

If the user wishes to use software to control the multiplexer select the Zynq PS\_MIO0 pin is utilized. When software controls the multiplexer select signal, the running application can select either eMMC accesses for the Zynq or standard MIO interfaces via the JX2 connector. When using software to control the multiplexer select signal, the JX2 MIO interface becomes limited to 7 I/O pins, MIO[15:9] since the Zynq PS\_MIO0 pin is being used to control the multiplexer select signal. This option offers the user the most flexibility to connect either interface to the Zynq when needed by the application.

Software control of the Multiplexer Select signal is the default setting for the PicoZed 7010/7020 System-On-Module from the factory, and is enabled by the jumper resistor position at JT1 position 1-2.

In position 1-2 the Zyng PS\_MIO0 pin is connected to the multiplexer select pins of U1 and U2.

In position 2-3 the Zynq PS\_MIO0 pin is connected to the JX2 MIO0 pin via the multiplexer channel 4 on device U2.

#### Hardware Control of Multiplexer Select (Interface Strapping)

Another user option available is to "hard-wire" one of the two interfaces, JX2 MIO[0,15:9] or eMMC I/O to the Zynq PS\_MIO[0,15:9] pins. This can be done by modifying the resistor jumper position at JT2, which sets the desired interface and JT1, which controls the use of PS\_MIO0.

The default resistor jumper position for JT2 is 1-2, which selects the eMMC as the selected interface.

If JT2 resistor jumper position is changed to position 2-3, the JX2 MIO pins become selected by the multiplexers. In this case, it is best to also change the JT1 jumper position to 2-3 to ensure that a full 8-bit peripheral can be connected through the JX2 MIO interface if so desired.

The diagram below shows how the eMMC and JX2 MIO signals are connected to the Zynq via the multiplexer ICs U1 and U2.

Figure 2 – eMMC / JX2 MIO Multiplexer Block Diagram on PicoZed Revision C

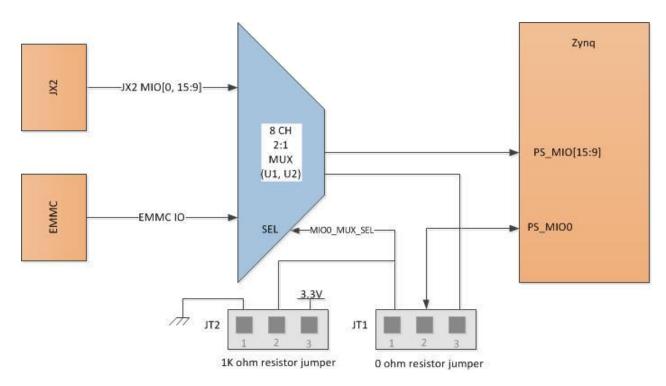

#### 2.2.3.2 Revision E Only

The eMMC connects to the Zynq PS via six MIO signals. On Revision E, these signals are routed directly to the eMMC through zero-ohm resistor jumpers. This means that from a hardware perspective, the eMMC is a direct connection to the Zynq MIO. This allows PicoZed to support high-speed mode at 50 MHz on the SDIO interface between Zynq and the eMMC.

#### Jumper Option to Enable MIOs on JX2 connector

It is possible "hard-wire" JX2 MIO[15:10] to the Zynq PS\_MIO[15:10] pins. This can be done by modifying the six resistor jumper positions at JT10 through JT15 as shown below. Note that PS\_MIO0 and PS\_MIO9 are permanently connected to JX2 on Rev E.

The default resistor jumper position for the JTxx jumpers are 1-2, which selects the eMMC as the selected interface. If you prefer the JTxx jumpers populated by default at 2-3, please contact your local Avnet FAE or <a href="mailto:customize@avnet.com">customize@avnet.com</a> for a custom option.

Figure 3 – Resistor Jumper Option to Choose eMMC or JX2 for MIO Connection

#### 2.3 USB 2.0 OTG

Zynq contains a hardened PS USB 2.0 controller. PicoZed 7010/7020 takes advantage of the USB 2.0 controller to provide USB 2.0 On-The-Go signaling to the JX3 connector.

PicoZed 7010/7020 implements one of the two available PS USB 2.0 interfaces. An external PHY with an 8-bit ULPI interface is implemented. A SMSC USB3320 Standalone USB Transceiver Chip is used as the PHY. The PHY features a complete HS-USB Physical Front-End supporting speeds of up to 480Mbs. VDDIO for this device can be 1.8V or 3.3V, and on the PicoZed 7010/7020 is powered at 1.8V. The PHY is connected to MIO Bank 1/501, which is also powered at 1.8V. This is critical since a level translator cannot be used as it would impact the tight ULPI timing required between the PHY and the Zyng device.

Additionally, the USB chip must clock the ULPI interface which requires a 24 MHz crystal or oscillator (configured as ULPI Output Clock Mode). On the PicoZed 7010/7020, the 24 MHz oscillator is an Abracon ASDMB CMOS oscillator, ASDMB-24.000MHZ-LC-T.

The USB connector is not populated on the PicoZed 7010/7020 System-on-Module and is designed to have the USB connector reside on the mating carrier card. The four USB connector signals (USB\_P, USB\_N, USB\_ID and USB\_OTG\_CPEN) are connected to the JX3 Micro Header. The table below shows the connections of these four signals at JX3.

| Signal Name  | JX3 Pin |

|--------------|---------|

| USB_OTG_N    | 69      |

| USB_OTG_P    | 67      |

| USB_ID       | 63      |

| USB OTG CPEN | 70      |

Table 4 - USB 2.0 JX3 Pin Assignments

If using the Avnet PicoZed FMC Carrier Card as the mating carrier card, a Micro-AB connector provided by FCI is used. The FCI part number is 10104111-0001LF.

The usb0 peripheral is used on the PS, connected through MIO[28-39] in MIO Bank 1/501. The USB Reset signal is connected to MIO[7]. Signal PS\_MIO7 is a 3.3V signal. It is AND-ed with the power-on reset (PG\_MODULE) signal and then level shifted to 1.8V through a TI TXS0102 level translator before connecting to the USB3320 Pin 27 RESET.

PicoZed 7010/7020 is configured such that either Host Mode (OTG) or Device Mode can be used depending on the circuitry of the carrier card. With a standard connection to a baseboard (no power supply used to provide USB power to the connector) the device will operate in Device Mode. Using the USB\_OTG\_CPEN signal on JX3 allows the user to control an external power source for USB VBUS on the carrier card. Other considerations need to be made to accommodate Host Mode. Refer to the Avnet PicoZed FMC Carrier Card design for an example design for configuring the carrier card for either Host Mode or Device Mode.

| Signal Name | Description                             | Zynq Bank      | MIO   | SMSC 3320 Pin |

|-------------|-----------------------------------------|----------------|-------|---------------|

| Data[7:0]   | USB Data lines                          | MIO Bank 1/501 |       | Data[7:0]     |

| CLKOUT      | CLKOUT USB Clock                        |                |       | 1             |

| DIR         | ULPI DIR output signal                  | MIO Bank 1/501 | 28:39 | 31            |

| STP         | STP ULPI STP input signal               |                |       | 29            |

| NXT         | ULPI NXT output signal                  | MIO Bank 1/501 |       | 2             |

| REFSEL[2:0] | USB Chip Select                         |                |       | 8,11,14       |

| DP          | DP pin of USB Connector                 | N/C            | N/C   | 18            |

| DM          | DM pin of USB Connector                 | N/C            | N/C   | 19            |

| ID          | Identification pin of the USB connector |                |       | 23            |

| RESET_B     | Reset                                   | MIO Bank 1/501 | 7**   | 27**          |

Table 5 - USB 2.0 Pin Assignment and Definitions

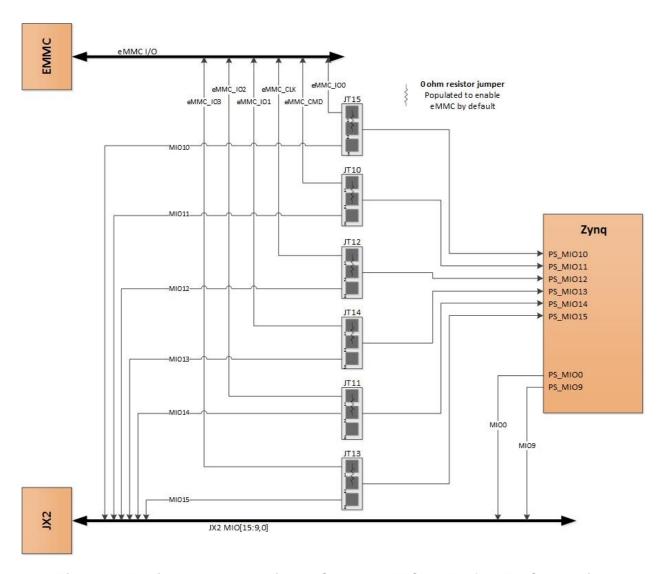

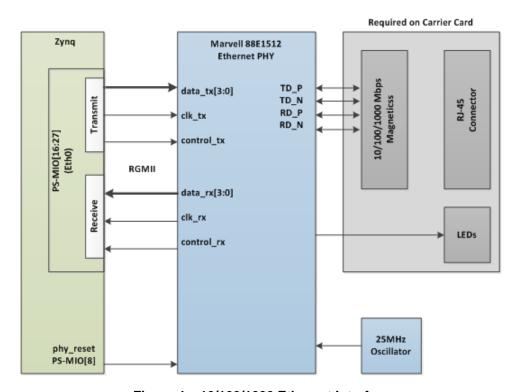

#### 2.4 10/100/1000 Ethernet PHY

PicoZed 7010/7020 implements a 10/100/1000 Ethernet port for network connection using a Marvell 88E1512 PHY. This part operates at 1.8V. The PHY connects to MIO Bank 1/501 (1.8V) and interfaces to the Zynq-7000 AP SoC via RGMII.

The RJ-45 interface signals are connected to the JX3 Micro Header.

A high-level block diagram the 10/100/1000 Ethernet interface is shown in the following figure.

Figure 4 – 10/100/1000 Ethernet Interface

<sup>\*\*</sup> Connected through AND-gate with PG\_MODULE through level translator (TI TXS0102DQE).

Zynq requires a voltage reference for RGMII interfaces. Thus PS\_MIO\_VREF, E11, is tied to 0.9V, half the bank voltage of MIO Bank 1/501. The 0.9V is generated through a resistor divider.

The 88E1512 also requires a 25 MHz input clock. An ABRACON ASDMB-25.000MHZ-LC-T is used as this reference.

| Signal Name | Description      | Zynq pin                                         | MIO   | 88E1512 pin          |

|-------------|------------------|--------------------------------------------------|-------|----------------------|

| RX_CLK      | Receive Clock    | B17                                              |       | 46                   |

| RX_CTRL     | Receive Control  | D13                                              |       | 43                   |

| RXD[3:0]    | Receive Data     | RXD0: D11<br>RXD1: A16<br>RXD2: F15<br>RXD3: A15 | 16:27 | 44<br>45<br>47<br>48 |

| TX_CLK      | Transmit Clock   | A19                                              | 10.27 | 53                   |

| TX_CTRL     | Transmit Control | F14                                              |       | 56                   |

| TXD[3:0]    | Transmit Data    | TXD0: E14<br>TXD1: B18<br>TXD2: D10<br>TXD3: A17 |       | 50<br>51<br>54<br>55 |

| MDIO        | Management Data  | C11                                              | 53    | 8                    |

| MDC         | Management Clock | C10                                              | 52    | 7                    |

| ETH_RST_N   | PHY Reset        | B14                                              | 47**  | 16 **                |

Table 6 - Ethernet PHY Pin Assignment and Definitions

The datasheet for the Marvell 88E1512 is not available publicly. An NDA is required for this information. Please contact your local Avnet or Marvell representative for assistance.

<sup>\*\*</sup> Requires a resistor change to the board to use PHY Reset. By default MIO47 is routed to JX3.

#### 2.5 User I/O

#### 2.5.1 Available PS MIO User Pins

PicoZed 7010/7020 provides 8 user PS MIO pins from bank 500 and 12 user PS MIO pins from bank 501 of the Zynq-7000 AP SoC. The 20 PS MIO pins connect to the Zynq Processor Sub-System for the implementation of peripheral such as USB, SPI, SDIO, CAN, UART, and I2C. These I/O pins can also be used as general purpose IO to connect push buttons, LEDs and/or switches to the Zynq from the carrier card.

**Note:** The bank 500 PS MIO are shared with the eMMC interface and proper operation of these 8 user PS MIO pins depends on the multiplexer implemented to support the shared interface. Please review section 2.2.3 eMMC (Multi-Media Controller) for details on the multiplexer interface.

| Signal Name | Zynq Pin           | JX Pin |

|-------------|--------------------|--------|

| PS_MIO0     | E6 (MIO Bank 500)  | JX2.7  |

| PS_MIO9     | B5 (MIO Bank 500)  | JX2.8  |

| PS_MIO10    | E9 (MIO Bank 500)  | JX2.1  |

| PS_MIO11    | C6 (MIO Bank 500)  | JX2.6  |

| PS_MIO12    | D9 (MIO Bank 500)  | JX2.5  |

| PS_MIO13    | E8 (MIO Bank 500)  | JX2.2  |

| PS_MIO14    | C5 (MIO Bank 500)  | JX2.3  |

| PS_MIO15    | C8 (MIO Bank 500)  | JX2.4  |

|             |                    |        |

| PS_MIO40    | D14 (MIO Bank 501) | JX3.43 |

| PS_MIO41    | C17 (MIO Bank 501) | JX3.34 |

| PS_MIO42    | E12 (MIO Bank 501) | JX3.37 |

| PS_MIO43    | A9 (MIO Bank 501)  | JX3.36 |

| PS_MIO44    | F13 (MIO Bank 501) | JX3.39 |

| PS_MIO45    | B15 (MIO Bank 501) | JX3.38 |

| PS_MIO46    | D16 (MIO Bank 501) | JX3.41 |

| PS_MIO47    | B14 (MIO Bank 501) | JX3.40 |

| PS_MIO48    | B12 (MIO Bank 501) | JX3.42 |

| PS_MIO49    | C12 (MIO Bank 501) | JX3.44 |

| PS_MIO50    | B13 (MIO Bank 501) | JX3.66 |

| PS_MIO51    | B9 (MIO Bank 501)  | JX3.64 |

|             |                    |        |

Table 7 - PS MIO User Interface

#### 2.5.2 Available PL IO User Pins

PicoZed 7010/7020 provides 50 user PL IO pins from bank 34, 50 user PL IO pins from bank 35 of the Zynq-7000 AP SoC. Additionally, the PicoZed 7020 version provides access to 25 more user PL IO pins from bank 13. The 100 PL IO pins on the PicoZed 7010 and the 125 PL IO pins on the PicoZed 7020 connect to the Zynq Programmable Logic Sub-System for user implementation of any feasible interface.

The PL IO pins were routed with matched lengths to each of the JX connectors. The matched pairs, noted by "LVDS" in the net name of Tables 10, 11, and 12 may be used as either single ended I/O or differential pairs depending on the end users design requirements.

Use of these signals for various interfaces depends on the bank voltages assigned. The end user carrier card is responsible for providing VCCO for bank 34, bank 35, and bank13 depending on what it being implemented and whether you are using PicoZed 7010 or PicoZed 7020.

It is recommended that any custom interface to be implemented be run through the Vivado tool suite for a sanity check on place and route and timing closure in advance of end user carrier card manufacturing.

Pin out details of the available PL IO are included in section 2.8: Expansion Headers.

#### 2.6 Clock Source

The PicoZed 7010/7020 connects a dedicated 33.3333 MHz clock source to the Zynq-7000 AP SoC's PS. An ABRACON ASDMB-33.333MHZ-LC-T or similar oscillator with 40-ohm series termination is used. The PS infrastructure can generate up to four PLL-based clocks for the PL system.

#### 2.7 Reset Sources

#### 2.7.1 Zynq Power-on Reset (PS\_POR\_B)

The Zynq PS supports an external power-on reset signal. The power-on reset is the master reset of the entire chip. This signal resets every register in the device capable of being reset. On PicoZed 7010/7020 this signal is labelled PG\_MODULE and it is connected to the power good output of the final stage of the power regulation circuitry. These power supplies have open drain outputs that pull this signal low until the output voltage is valid. If an expansion card is connected to PicoZed 7010/7020, the expansion card should also wire-OR to this net and not release it until the expansion card power is also good. Review the PicoZed 7010/7020 schematic for other devices that are reset by the PG\_MODULE open drain signal.

To stall Zynq boot-up, this signal should be held low. No other signal (PS\_SRST\_B, PROGRAM B, or INIT B) is capable of doing this as in other Xilinx FPGA architectures.

#### 2.7.2 PROGRAM\_B, DONE, PUDC\_B, INIT\_B Pins

INIT\_B, PROGRAM\_B and PUDC\_B all have pull-up resistors to appropriate voltages applied to them. The INIT\_B, PUDC\_B and DONE signals are routed to the carrier card via the Micro Headers, JX1 and JX2.

There is not a DONE LED indicator on the PicoZed 7010/7020 System-On-Module. When PL configuration is complete DONE will go high. It is recommended that the DONE signal be connected to an LED on the carrier card to indicate when the FPGA configuration is complete.

When mating to the Avnet PicoZed FMC Carrier Card a blue LED labelled DONE will illuminate.

#### 2.7.3 Processor Subsystem Reset

System reset, labelled PS\_SRST\_B, resets the processor as well as erases all debug configurations. The external system reset allows the user to reset all of the functional logic within the device without disturbing the debug environment. For example, the previous break points set by the user remain valid after system reset. Due to security concerns, system reset erases all memory content within the PS, including the OCM. The PL is also reset in system reset. System reset does not re-sample the boot mode strapping pins.

This active-low signal can be asserted via the carrier card through the Micro Header interface.

**Note:** This signal cannot be asserted while the boot ROM is executing following a POR reset. If PS\_SRST\_B is asserted while the boot ROM is running through a POR reset sequence it will trigger a lock-down event preventing the boot ROM from completing. To recover from lockdown the device either needs to be power cycled or PS\_POR\_B needs to be asserted.

#### 2.8 Expansion Headers

#### 2.8.1 Micro Headers

PicoZed 7010/7020 features three 100-pin Micro Headers (FCI, 61082-101400LF) for connection to expansion cards.

The JX1 and JX2 connectors interface PL, PS I/O to the expansion card as well as two dedicated analog inputs, the four dedicated JTAG signals, power and control signals. The JX3 connector interfaces to peripheral interfaces such as Ethernet, USB 2.0, 10 Bank 13 PL I/O (Zyng 7020 devices), and 12 Zyng PS MIO.

The connectors are FCI 0.8mm Bergstak®, 100 Position, Dual Row, BTB Vertical Receptacles. These have variable stack heights from 5mm to 16mm, making it easy to connect to a variety of expansion or system boards. Each pin can carry 500mA of current and support I/O speeds in excess of what Zyng can achieve.

PicoZed 7010/7020 does not power the PL VCCIO banks. This is required to be provided by the carrier card. This gives the carrier card the flexibility to control the I/O bank voltages. Separate routes/planes are used for VCCO\_34 and VCCO\_35 such that the carrier card could potentially power these independently. The PicoZed 7010 has two PL I/O banks. Banks 34 and 35 each contain 50 I/O. The PicoZed 7020 contains a third PL I/O bank. Bank 13 is fully connected (25 I/O) on the PicoZed 7020. Bank 13's power has an independent rail, VCCO\_13, which is powered from the carrier card as well.

Within a PL I/O Bank 34 or Bank 35, there are 50 I/O capable of up to 24 differential pairs per bank. Differential LVDS pairs on a -1 speed grade device are capable of 950Mbps of DDR data. Each differential pair from Bank 34 and 35 is isolated by a power or ground pin. Additionally, eight of these I/O can be connected as clock inputs (four MRCC and four SRCC inputs). Each PL bank can also be configured to be a memory interface with up to four dedicated DQS data strobes and data byte groups. Bank 35 adds the capability to use the I/O to interface up to 16 differential analog inputs. One of the differential pairs (JX1\_LVDS\_2\_P) in Bank 34 is shared with PUDC\_B.

The diagrams listed below illustrate the connections on the Micro Headers.

|          | Micro Heade                         | er #1 (JX1)                |      |          | Micro Heade                    | er #2 (JX2)   |      |

|----------|-------------------------------------|----------------------------|------|----------|--------------------------------|---------------|------|

|          | Signal Name                         | Source                     | Pins |          | Signal Name                    | Source        | Pins |

| 7        | Bank 34 I/Os<br>(Except for PUDC_B) | Zynq Bank 34               | 49   |          | Bank 35 I/Os                   | Zynq Bank 35  | 50   |

| <u> </u> | Bank 13 pins<br>(PicoZed 7020)      | Bank 13                    | 8    | <u> </u> | Bank 13 pins<br>(PicoZed 7020) | Bank 13       | 7    |

|          | TMS_0                               | Zynq Bank 0                | 5    | PS       | PS Pmod MIO[0,9-15]            | Zynq Bank 500 | 8    |

| JTAG     | TDI_0<br>TCK_0                      | Zynq Bank 0<br>Zynq Bank 0 | ပ    |          | Init_B_0                       | Zynq Bank 0   | 1    |

| ب        | TDO_0                               | Zynq Bank 0                |      |          | PG_1V8                         | Expansion     | 1    |

|          | Carrier_SRST#                       | Expansion                  |      |          | PG_MODULE                      | Expansion     | 1    |

|          | VP_0                                | Zynq Bank 0                | 4    | ver      | Vin                            | Expansion     | 5    |

| Analog   | VN_0                                | Zynq Bank 0                |      | Power    | GND                            | Expansion     | 23   |

| Ana      | DXP_0                               | Zynq Bank 0                |      |          | VCCO_35                        | Expansion     | 3    |

|          | DXN_0                               | Zynq Bank 0                |      |          | VCCO_13                        | Expansion     | 1    |

| ပ        | FPGA_DONE                           | Zynq Bank 0                | 2    |          |                                | TOTAL         | 100  |

|          | PUDC_B / IO                         | Zynq Bank 34               |      |          |                                |               |      |

|          | PWR_Enable                          | Expansion                  | 1    |          |                                |               |      |

| <u></u>  | Vin                                 | Expansion                  | 4    |          |                                |               |      |

| Power    | GND                                 | Expansion                  | 23   |          |                                |               |      |

| Δ.       | VCCO_34                             | Expansion                  | 3    |          |                                |               |      |

|          | VBATT                               | Expansion                  | 1    |          |                                |               |      |

|          |                                     | TOTAL                      | 100  |          |                                |               |      |

Table 8 - Micro Header JX1 and JX2 Pin Outs

|          | Micro Header #3 (JX3)       |                             |      |  |  |  |  |  |  |  |

|----------|-----------------------------|-----------------------------|------|--|--|--|--|--|--|--|

|          | Signal Name                 | Source                      | Pins |  |  |  |  |  |  |  |

| చ        | Bank 13 I/Os (PicoZed 7020) | Zynq Bank 13 (PicoZed 7020) | 20*  |  |  |  |  |  |  |  |

|          | Ethernet I/O                | 501                         | 10   |  |  |  |  |  |  |  |

| PS       | USB I/O                     | 501                         | 4    |  |  |  |  |  |  |  |

|          | PS MIO[40-51]               | Zynq Bank 501               | 12   |  |  |  |  |  |  |  |

| MGT      | (No Connect)                | No Connect                  | 20   |  |  |  |  |  |  |  |

|          | MGT_AVCC (No Connect)       | No Connect                  | 4    |  |  |  |  |  |  |  |

| _        | MGTAVTT (No Connect)        | No Connect                  | 2    |  |  |  |  |  |  |  |

| Роме     | VCCO_13                     | Expansion                   | 2    |  |  |  |  |  |  |  |

| <u> </u> | GND                         | Expansion                   | 25   |  |  |  |  |  |  |  |

|          | USB_VBUS_OTG                | Expansion                   | 1    |  |  |  |  |  |  |  |

|          |                             | TOTAL                       | 100  |  |  |  |  |  |  |  |

Table 9 - Micro Header JX3 Pin Out

<sup>\*</sup> PicoZed 7020 only populates 10 out of 20 JX3 IO Dedicated to Bank 13 Signals

| PicoZed<br>7010/7020 Pin # | Net<br>Name     | JX1<br>Pin # | JX1<br>Pin # | Net<br>Name                  | PicoZed<br>7010/7020 Pin # |

|----------------------------|-----------------|--------------|--------------|------------------------------|----------------------------|

| 0 - F9                     | JTAG_TCK        | 1            | 2            | JTAG_TMS                     | 0 - J6                     |

| 0 - F6                     | JTAG_TDO        | 3            | 4            | JTAG_TDI                     | 0 - G6                     |

| N/A                        | PWR_ENABLE      | 5            | 6            | CARRIER_SRST#                | 501 - B10                  |

| 0 - F11                    | FPGA_VBATT      | 7            | 8            | FPGA_DONE                    | 0 - R11                    |

| 34 - R19                   | JX1_SE_0        | 9            | 10           | JX1_SE_1                     | 34 - T19                   |

| 34 - T11                   | JX1_LVDS_0_P    | 11           | 12           | JX1_LVDS_1_P                 | 34 - T12                   |

| 34 - T10                   | JX1_LVDS_0_N    | 13           | 14           | JX1_LVDS_1_N                 | 34 - U12                   |

| N/A                        | GND             | 15           | 16           | GND                          | N/A                        |

| 34 - U13                   | JX1_LVDS_2_P    | 17           | 18           | JX1_LVDS_3_P                 | 34 - V12                   |

| 34 - V13                   | JX1_LVDS_2_N    | 19           | 20           | JX1_LVDS_3_N                 | 34 - W13                   |

| N/A                        | GND             | 21           | 22           | GND                          | N/A                        |

| 34 - T14                   | JX1 LVDS 4 P    | 23           | 24           | JX1_LVDS_5_P                 | 34 - P14                   |

| 34 - T15                   | JX1_LVDS_4_N    | 25           | 26           | JX1_LVDS_5_N                 | 34 - R14                   |

| N/A                        | GND             | 27           | 28           | GND                          | N/A                        |

| 34 - Y16                   | JX1_LVDS_6_P    | 29           | 30           | JX1_LVDS_7_P                 | 34 - W14                   |

|                            |                 | 31           | 32           | JX1_LVDS_7_P<br>JX1_LVDS_7_N | 34 - Y14                   |

| 34 - Y17                   | JX1_LVDS_6_N    |              |              |                              |                            |

| N/A                        | GND             | 33           | 34           | GND                          | N/A<br>34 - V15            |

| 34 - T16                   | JX1_LVDS_8_P    | 35           | 36           | JX1_LVDS_9_P                 |                            |

| 34 - U17                   | JX1_LVDS_8_N    | 37           | 38           | JX1_LVDS_9_N                 | 34 - W15                   |

| N/A                        | GND             | 39           | 40           | GND                          | N/A                        |

| 34 - U14                   | JX1_LVDS_10_P   | 41           | 42           | JX1_LVDS_11_P                | 34 - U18                   |

| 34 - U15                   | JX1_LVDS_10_N   | 43           | 44           | JX1_LVDS_11_N                | 34 - U19                   |

| N/A                        | GND             | 45           | 46           | GND                          | N/A                        |

| 34 - N18                   | JX1_LVDS_12_P   | 47           | 48           | JX1_LVDS_13_P                | 34 - N20                   |

| 34 - P19                   | JX1_LVDS_12_N   | 49           | 50           | JX1_LVDS_13_N                | 34 - P20                   |

| N/A                        | GND             | 51           | 52           | GND                          | N/A                        |

| 34 - T20                   | JX1_LVDS_14_P   | 53           | 54           | JX1_LVDS_15_P                | 34 - V20                   |

| 34 - U20                   | JX1_LVDS_14_N   | 55           | 56           | JX1_LVDS_15_N                | 34 - W20                   |

| N/A                        | VIN_HDR         | 57           | 58           | VIN_HDR                      | N/A                        |

| N/A                        | VIN_HDR         | 59           | 60           | VIN_HDR                      | N/A                        |

| 34 - Y18                   | JX1_LVDS_16_P   | 61           | 62           | JX1_LVDS_17_P                | 34 - V16                   |

| 34 - Y19                   | JX1_LVDS_16_N   | 63           | 64           | JX1_LVDS_17_N                | 34 - W16                   |

| N/A                        | GND             | 65           | 66           | GND                          | N/A                        |

| 34 - R16                   | JX1_LVDS_18_P   | 67           | 68           | JX1_LVDS_19_P                | 34 - T17                   |

| 34 - R17                   | JX1_LVDS_18_N   | 69           | 70           | JX1_LVDS_19_N                | 34 - R18                   |

| N/A                        | GND             | 71           | 72           | GND                          | N/A                        |

| 34 - V17                   | JX1_LVDS_20_P   | 73           | 74           | JX1_LVDS_21_P                | 34 - W18                   |

| 34 - V18                   | JX1_LVDS_20_N   | 75           | 76           | JX1_LVDS_21_N                | 34 - W19                   |

| N/A                        | GND             | 77           | 78           | VCCO_34                      | N/A                        |

| N/A                        | VCCO_34         | 79           | 80           | VCCO_34                      | N/A                        |

| 34 - N17                   | JX1_LVDS_22_P   | 81           | 82           | JX1_LVDS_23_P                | 34 - P15                   |

| 34 - P18                   | JX1_LVDS_22_N   | 83           | 84           | JX1_LVDS_23_N                | 34 - P16                   |

| N/A                        | GND             | 85           | 86           | GND                          | N/A                        |

| 13 - U7                    | BANK13_LVDS_0_P | 87           | 88           | BANK13_LVDS_1_P              | 13 - T9                    |

| 13 - V7                    | BANK13_LVDS_0_N | 89           | 90           | BANK13_LVDS_1_N              | 13 - U10                   |

| 13 - V8                    | BANK13_LVDS_2_P | 91           | 92           | BANK13_LVDS_3_P              | 13 - T5                    |

| 13 - W8                    | BANK13_LVDS_2_N | 93           | 94           | BANK13_LVDS_3_N              | 13 - U5                    |

| N/A                        | GND             | 95           | 96           | GND                          | N/A                        |

| 0 - K9                     | VP_0_P          | 97           | 98           | DXP_0_P                      | 0 - M9                     |

| 0 - L10                    | VN_0_N          | 99           | 100          | DXN_0_N                      | 0 - M10                    |

Table 10 – JX1 Connections

| PicoZed<br>7010/7020 Pin # | PicoZed<br>Net  | JX2<br>Pin # | JX2<br>Pin # | PicoZed<br>Net  | PicoZed<br>7010/7020 Pin # |

|----------------------------|-----------------|--------------|--------------|-----------------|----------------------------|

| 500 - E9                   | PS_MIO10        | 1            | 2            | PS_MIO13        | 500 – E8                   |

| 500 - C5                   | PS_MIO14        | 3            | 4            | PS_MIO15        | 500 – C8                   |

| 500 - D9                   | PS_MIO12        | 5            | 6            | PS_MIO11        | 500 – C6                   |

| 500 - E6                   | PS_MIO0         | 7            | 8            | PS_MIO9         | 500 – B5                   |

| 0 - R10                    | INIT#           | 9            | 10           | VCCIO_EN        | N/A                        |

| 500 - C7                   | PG_MODULE       | 11           | 12           | VIN_HDR         | N/A                        |

| 35 - G14                   | JX2_SE_0        | 13           | 14           | JX2 SE 1        | 35 - J15                   |

| N/A                        | GND             | 15           | 16           | GND             | N/A                        |

| 35 - C20                   | JX2_LVDS_0_P    | 17           | 18           | JX2_LVDS_1_P    | 35 - B19                   |

| 35 - B20                   | JX2_LVDS_0_N    | 19           | 20           | JX2_LVDS_1_N    | 35 - A20                   |

| N/A                        | GND             | 21           | 22           | GND             | N/A                        |

| 35 - E17                   | JX2_LVDS_2_P    | 23           | 24           | JX2_LVDS_3_P    | 35 - D19                   |

| 35 - D18                   | JX2_LVDS_2_N    | 25           | 26           | JX2_LVDS_3_N    | 35 - D20                   |

| N/A                        | GND             | 27           | 28           | GND             | N/A                        |

| 35 - E18                   | JX2_LVDS_4_P    | 29           | 30           | JX2_LVDS_5_P    | 35 - F16                   |

| 35 - E19                   | JX2_LVDS_4_N    | 31           | 32           | JX2 LVDS 5 N    | 35 - F17                   |

| N/A                        | GND             | 33           | 34           | GND             | N/A                        |

| 35 - L19                   | JX2_LVDS_6_P    | 35           | 36           | JX2_LVDS_7_P    | 35 - M19                   |

| 35 - L20                   | JX2_LVDS_6_N    | 37           | 38           | JX2_LVDS_7_N    | 35 - M20                   |

| N/A                        | GND             | 39           | 40           | GND             | N/A                        |

| 35 - M17                   | JX2_LVDS_8_P    | 41           | 42           | JX2_LVDS_9_P    | 35 - K19                   |

| 35 - M18                   | JX2_LVDS_8_N    | 43           | 44           | JX2_LVDS_9_N    | 35 - J19                   |

| N/A                        | GND             | 45           | 46           | GND             | N/A                        |

| 35 - L16                   | JX2_LVDS_10_P   | 47           | 48           | JX2_LVDS_11_P   | 35 - K17                   |

| 35 - L17                   | JX2_LVDS_10_N   | 49           | 50           | JX2_LVDS_11_N   | 35 - K18                   |

| N/A                        | GND             | 51           | 52           | GND             | N/A                        |

| 35 - H16                   | JX2_LVDS_12_P   | 53           | 54           | JX2 LVDS 13 P   | 35 - J18                   |

| 35 - H17                   | JX2_LVDS_12_N   | 55           | 56           | JX2_LVDS_13_N   | 35 - H18                   |

| N/A                        | VIN_HDR         | 57           | 58           | VIN_HDR         | N/A                        |

| N/A                        | VIN_HDR         | 59           | 60           | VIN_HDR         | N/A                        |

| 35 - G17                   | JX2_LVDS_14_P   | 61           | 62           | JX2_LVDS_15_P   | 35 - F19                   |

| 35 - G18                   | JX2_LVDS_14_N   | 63           | 64           | JX2_LVDS_15_N   | 35 - F20                   |

| N/A                        | GND             | 65           | 66           | GND             | N/A                        |

| 35 - G19                   | JX2_LVDS_16_P   | 67           | 68           | JX2_LVDS_17_P   | 35 - J20                   |

| 35 - G20                   | JX2_LVDS_16_N   | 69           | 70           | JX2_LVDS_17_N   | 35 - H20                   |

| N/A                        | GND             | 71           | 72           | GND             | N/A                        |

| 35 - K14                   | JX2_LVDS_18_P   | 73           | 74           | JX2_LVDS_19_P   | 35 - H15                   |

| 35 - J14                   | JX2_LVDS_18_N   | 75           | 76           | JX2_LVDS_19_N   | 35 - G15                   |

| N/A                        | GND             | 77           | 78           | VCCO_35         | N/A                        |

| N/A                        | VCCO_35         | 79           | 80           | VCCO_35         | N/A                        |

| 35 - N15                   | JX2_LVDS_20_P   | 81           | 82           | JX2_LVDS_21_P   | 35 - L14                   |

| 35 - N16                   | JX2_LVDS_20_N   | 83           | 84           | JX2_LVDS_21_N   | 35 - L15                   |

| N/A                        | GND             | 85           | 86           | GND             | N/A                        |

| 35 - M14                   | JX2_LVDS_22_P   | 87           | 88           | JX2_LVDS_23_P   | 35 - K16                   |

| 35 - M15                   | JX2_LVDS_22_N   | 89           | 90           | JX2_LVDS_23_N   | 35 - J16                   |

| N/A                        | GND             | 91           | 92           | GND             | N/A                        |

| 13 - Y12                   | BANK13_LVDS_4_P | 93           | 94           | BANK13_LVDS_5_P | 13 - V11                   |

| 13 - Y13                   | BANK13_LVDS_4_N | 95           | 96           | BANK13_LVDS_5_N | 13 - V10                   |

| 13 - V6                    | BANK13_LVDS_6_P | 97           | 98           | VCCO_13         | N/A                        |

| 13 - W6                    | BANK13_LVDS_6_N | 99           | 100          | BANK13_SE_0     | 13 - V5                    |

Table 11 – JX2 Connections

| PicoZed<br>7010/7020 Pin # | PicoZed<br>Net   | JX3<br>Pin # | JX3<br>Pin # | PicoZed<br>Net   | PicoZed<br>7010/7020 Pin # |

|----------------------------|------------------|--------------|--------------|------------------|----------------------------|

| N/A                        | MGTREFCLK0_P     | 1            | 2            | MGTREFCLK1_P     | N/A                        |

| N/A                        | MGTREFCLK0_N     | 3            | 4            | MGTREFCLK1_N     | N/A                        |

| N/A                        | MGTAVCC          | 5            | 6            | GND              | N/A                        |

| N/A                        | MGTAVCC          | 7            | 8            | MGTRX0_P         | N/A                        |

| N/A                        | MGTAVCC          | 9            | 10           | MGTRX0_N         | N/A                        |

| N/A                        | MGTAVCC          | 11           | 12           | GND              | N/A                        |

| N/A                        | MGTTX0_P         | 13           | 14           | MGTRX1_P         | N/A                        |

| N/A                        | MGTTX0_N         | 15           | 16           | MGTRX1_N         | N/A                        |

| N/A                        | GND              | 17           | 18           | GND              | N/A                        |

| N/A                        | MGTTX1_P         | 19           | 20           | MGTRX2_P         | N/A                        |

| N/A                        | MGTTX1_N         | 21           | 22           | MGTRX2_N         | N/A                        |

| N/A                        | GND              | 23           | 24           | GND              | N/A                        |

| N/A                        | MGTTX2_P         | 25           | 26           | MGTRX3_P         | N/A                        |

| N/A                        | MGTTX2_N         | 27           | 28           | MGTRX3_N         | N/A                        |

| N/A                        | GND              | 29           | 30           | MGTAVTT          | N/A                        |

| N/A                        | MGTTX3_P         | 31           | 32           | MGTAVTT          | N/A                        |

| N/A                        | MGTTX3_N         | 33           | 34           | PS_MIO41         | 501 – C17                  |

| N/A                        | GND              | 35           | 36           | PS_MIO43         | 501 – A9                   |

| 501 – E12                  | PS_MIO42         | 37           | 38           | PS_MIO45         | 501 – B15                  |

| 501 – F13                  | PS_MIO44         | 39           | 40           | PS_MIO47         | 501 – B13                  |

| 501 – D16                  | PS_MIO44         | 41           | 42           | PS_MIO47         | 501 – B12                  |

| 501 – D16                  | PS_MIO40         | 43           | 44           | PS_MIO49         | 501 – C12                  |

| N/A                        | VCCO_13          | 45           | 46           | VCCO_13          | N/A                        |

|                            |                  |              |              |                  |                            |

| N/A                        | ETH_PHY_LED0     | 47           | 48           | ETH_PHY_LED1     | N/A                        |

| N/A                        | GND              | 49           | 50           | GND              | N/A                        |

| N/A                        | ETH_MD1_P        | 51           | 52           | ETH_MD2_P        | N/A                        |

| N/A                        | ETH_MD1_N        | 53           | 54           | ETH_MD2_N        | N/A                        |

| N/A                        | GND              | 55           | 56           | GND              | N/A                        |

| N/A                        | ETH_MD3_P        | 57           | 58           | ETH_MD4_P        | N/A                        |

| N/A                        | ETH_MD3_N        | 59           | 60           | ETH_MD4_N        | N/A                        |

| N/A                        | GND              | 61           | 62           | GND              | N/A                        |

| N/A                        | USB_OTG_ID       | 63           | 64           | PS_MIO51         | 501 – B9                   |

| N/A                        | GND              | 65           | 66           | PS_MIO50         | 501 – B13                  |

| N/A                        | USB_OTG_P        | 67           | 68           | USB_VBUS_OTG     | N/A                        |

| N/A                        | USB_OTG_N        | 69           | 70           | USB_OTG_CPEN     | N/A                        |

| N/A                        | GND              | 71           | 72           | GND              | N/A                        |

| 13-Y7                      | BANK13_LVDS_7_P  | 73           | 74           | BANK13_LVDS_8_P  | 13-Y9                      |

| 13-Y6                      | BANK13_LVDS_7_N  | 75           | 76           | BANK13_LVDS_8_N  | 13-Y8                      |

| N/A                        | GND              | 77           | 78           | GND              | N/A                        |

| 13-W10                     | BANK13_LVDS_9_P  | 79           | 80           | BANK13_LVDS_10_P | 13-U9                      |

| 13-W9                      | BANK13_LVDS_9_N  | 81           | 82           | BANK13_LVDS_10_N | 13-U8                      |

| N/A                        | GND              | 83           | 84           | GND              | N/A                        |

| 13-W11                     | BANK13_LVDS_11_P | 85           | 86           | BANK13_LVDS_12_P | N/A                        |

| 13-Y11                     | BANK13_LVDS_11_N | 87           | 88           | BANK13_LVDS_12_N | N/A                        |

| N/A                        | GND              | 89           | 90           | GND              | N/A                        |

| N/A                        | BANK13_LVDS_13_P | 91           | 92           | BANK13_LVDS_14_P | N/A                        |

| N/A                        | BANK13_LVDS_13_N | 93           | 94           | BANK13_LVDS_14_N | N/A                        |

| N/A                        | GND              | 95           | 96           | GND              | N/A                        |

| N/A                        | BANK13_LVDS_15_P | 97           | 98           | BANK13_LVDS_16_P | N/A                        |

| N/A                        | BANK13_LVDS_15_N | 99           | 100          | BANK13_LVDS_16_N | N/A                        |

Table 12 - JX3 Connections

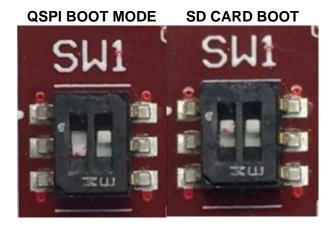

#### 2.9 Configuration Modes

Zynq-7000 AP SoC devices use a multi-stage boot process that supports both non-secure and secure boot. The PS is the master of the boot and configuration process. Upon reset, the device mode pins are read to determine the primary boot device to be used: NOR, NAND, Quad-SPI, SD Card or JTAG. PicoZed 7010/7020 allows 3 of those boot devices: QSPI is the default, while SD Card and JTAG boot are easily accessible by changing switch settings.

Note: SD Card and JTAG interfaces should be implemented on the end user carrier card.

Zyng has Voltage Mode pins, which are fixed on PicoZed 7010/7020

The boot mode pins are shared with MIO[8:2]. The usage of these mode pins can be and are used as follows:

- MIO[2] / Boot\_Mode[3]

- sets the JTAG mode

- MIO[5:3] / Boot\_Mode[2:0]

- select the boot mode

- Boot\_Mode[1] is fixed since it is only required for NOR boot, which is not supported on PicoZed 7010/7020

- MIO[6] / Boot Mode[4]

- enables the internal PLL

- fixed to 'enabled' on PicoZed 7010/7020

- MIO[8:7] / Vmode[1:0]

- configures the I/O bank voltages

- fixed on PicoZed 7010/7020

- MIO Bank 0 / 500 (MIO[7] / Vmode[0]) set to '0' for 3.3V

- MIO Bank 1 / 501 (MIO[8] / Vmode[1]) set to '1' for 1.8V

All mode pins are pulled either high or low through a 20 K $\Omega$  resistor that is either hard wired or connected to a switch or resistor jumper. By default, four mode signals are not jumper-adjustable and are populated as follows:

- MIO[3] / Boot Mode[1] is pulled low via 20 KΩ resistor.

- MIO[6] / Boot\_Mode[4] is pulled low via 20 KΩ resistor.

- MIO[7] / Vmode[0] is pulled low via 20 KΩ resistor.

- MIO[8] / Vmode[1] is pulled high via 20 KΩ resistor.

The other three mode signals, MIO[2], MIO[4] and MIO[5], are configurable via a jumper resistor or switch setting.

MIO[2] is pulled either high or low via a 0 ohm resistor jumper JT4. Default setting from the factory is pulled low (position 1-2) and puts the Zyng in Cascade JTAG mode.

MIO[5:4] is pulled high or low via a two channel dip switch SW1. Setting the switch positions will determine whether the Zynq boots from QSPI, the microSD card, or JTAG. Alternatively, the Revision E added resistor jumpers to make the mode setting permanent. SW1 can be depopulated in exchange for 0 ohm resistors at the JT8 (MIO4) and JT9 (MIO5) sites.

The table below shows the available boot mode configuration setting using JT4 and SW1.

| BOOT MODE       | JT4        | SW1 (1-3) / JT8    | SW1 (4-6) / JT9    |

|-----------------|------------|--------------------|--------------------|

| QSPI            | X          | LOW (2-3) / (2-3)  | HIGH (4-5) / (1-2) |

| SD CARD **      | X          | HIGH (1-2) / (1-2) | HIGH (4-5) / (1-2) |

| JTAG **         | X          | LOW (2-3) / (2-3)  | LOW (5-6) / (2-3)  |

| INDEP JTAG **   | HIGH (2-3) | LOW (2-3) / (2-3)  | LOW (5-6) / (2-3)  |

| CASCADE JTAG ** | LOW (1-2)  | LOW (2-3) / (2-3)  | LOW (5-6) / (2-3)  |

Table 13 - PicoZed 7010/7020 Configuration Modes

\*\*Interfaces on the End User's Carrier Card

Figure 5 – PicoZed 7010/7020 Boot Mode Switch

Expected configuration time using a 50MB/s QSPI flash is 250ms.

Zyng has many other configuration options; PicoZed 7010/7020 uses this configuration:

- V<sub>CCO 0</sub> is tied to 3.3V on PicoZed 7010/7020.

- PUDC\_B can be pulled high or low on PicoZed 7010/7020 via a resistor (JT5). This active-low input enables internal pull-ups during configuration on all SelectIO pins. By default, JT5 is populated with a 1K resistor in the 1-2 position, which pulls up PUDC\_B and disables the pull-ups during configuration. PUDC\_B is shared with Bank 34 I/O IO\_L3P and is connected to the Micro Header.

- Init\_B is pulled high via a 4.7KΩ resistor (RP2.2), but also connected to the Micro Header.

- Program\_B is pulled high via a 4.7KΩ resistor (RP2.4).

- CFGBVS is pulled high via a  $4.7K\Omega$  resistor (RP2.1).

The PS is responsible for configuring the PL. Zynq will not automatically reconfigure the PL as in standard FPGAs by toggling PROG. Likewise, it is not possible to hold off Zynq boot up with INIT\_B as this is now done with POR. If the application needs to reconfigure the PL, the software design must do this, or you can toggle POR to restart everything. When PL configuration is complete and the end user is using the Avnet PicoZed FMC Carrier Card, a blue LED will illuminate.

#### 2.9.1 JTAG Connections

PicoZed 7010/7020 requires an external JTAG cable connector populated on the carrier card for JTAG operations. JTAG signals are routed from Bank 0 of the Zynq to the Micro Header JX1. The following table shows the JTAG signal connections between the Zynq and the Micro Header.

The Zynq Bank 0 reference voltage, Vcco\_0, is connected to 3.3V. The JTAG Vref on the End User Carrier Card should be connected to 3.3V to ensure compatibility between the interfaces. For reference, see the PicoZed FMC Carrier Card schematics.

| SoC Pin # | PicoZed 7010/7020 Net | JX1 Pin# |

|-----------|-----------------------|----------|

| F9        | JTAG_TCK              | 1        |

| J6        | JTAG_TMS              | 2        |

| F6        | JTAG_TDO              | 3        |

| G6        | JTAG_TDI              | 4        |

Table 14 - JTAG Pin Connections

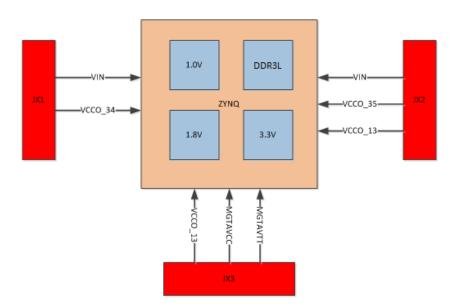

#### 2.10 Power Supplies

#### 2.10.1 Voltage Rails and Sources

PicoZed 7010/7020 is powered through the Micro Header connection between itself and the carrier card.

There are five regulators that reside on the PicoZed 7010/7020 that provide 1.0V, 1.35V, 1.8V, 3.3V and 0.675V power rails. These voltages are used to power the peripheral devices on the PicoZed System-On-Module. These regulators are powered from the end user carrier card via the VIN pins on the Micro Headers and are expected to carry 5V or 12V to the PicoZed System-On-Module for the input to the regulators.

There are also three bank voltages that are supplied from the end user carrier card to the PicoZed System-On-Module. Bank 34 (VCCO\_34), Bank 35 (VCCO\_35) and Bank 13 (VCCO\_13) are generated on the end user carrier card and connected to the PicoZed 7010/7020 System-On-Module via the Micro Headers. The voltage at which these banks operate is up to the carrier card design as all I/O that connect to these banks is exclusive to the Micro Headers (no on-board device is connected to these banks).

The diagram below shows a high level depiction of the power scheme for PicoZed 7010/7020 System-On-Module.

Figure 6 – PicoZed 7010/7020 Power Scheme

The table below shows the various voltage rails names on the schematic, the associated voltage for each rail, where they are connected on the Zynq 7010/7020, and where the voltage originates from.

| Schematic<br>Voltage Name | Voltage<br>Level | Zynq<br>Connection       | Voltage<br>Origination |  |  |

|---------------------------|------------------|--------------------------|------------------------|--|--|

|                           |                  | VCCINT                   |                        |  |  |

| 1.0V                      | 1.0V             | VCCBRAM                  |                        |  |  |

|                           |                  | VCCPINT                  |                        |  |  |

| VCCO_DDR3                 | 1.35V            | VCCO_DDR_502 (Bank 502)  |                        |  |  |

| VTTREF                    | 0.675\/          | PS_DDR_VREF0 (Bank 502)  |                        |  |  |

| VIIKEF                    | 0.675V           | PS_DDR_VREF1 (Bank 502)  | SOM                    |  |  |

|                           |                  | VCCO_MIO1_501 (Bank 501) |                        |  |  |

| 1.8V                      | 1.8V             | VCCAUX                   |                        |  |  |

|                           |                  | VCCPAUX                  |                        |  |  |

| 2.21/                     | 2.21/            | VCCO_0 (Bank 0)          |                        |  |  |

| 3.3V                      | 3.3V             | VCC_MIO0_500 (Bank 500)  |                        |  |  |

| VCCO_34                   | 1.8V/2.5V/3.3V   | VCCO_34 (Bank 34)        | JX1                    |  |  |

| VCCO_35                   | 1.8V/2.5V/3.3V   | VCCO_35 (Bank 35)        | JX2                    |  |  |

| VCCO_13                   | 1.8V/2.5V/3.3V   | VCCO_13 (Bank 13)        | JX2/JX3                |  |  |

Table 15 - PicoZed 7010/7020 Voltage Rails

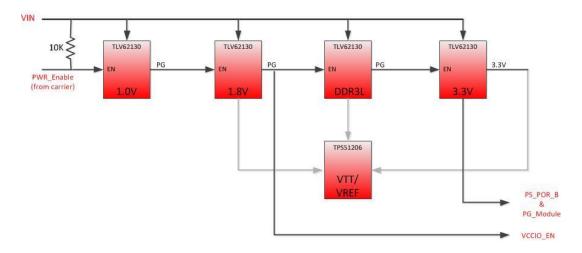

#### 2.10.2 Voltage Regulators

The following power solution provides the power rails of the PicoZed 7010/7020. Sequencing of the supplies is implemented by cascading the POWER GOOD outputs of each supply to the ENABLE input for the next supply in the sequence. 3.3V is the last supply to come up, therefore the POWER GOOD for the 3.3V supply is used to drive the PG\_MODULE net and is used as the power-on reset control for Zynq (U11.pin C7), Ethernet PHY (U4.pin 16), and USB-Host PHY (U5.pin 27).

This net is also connected to the Micro Headers so power supplies on the end user carrier card can also control this signal.

Figure 7 – Regulation Circuitry (VCCIO\_EN is PG\_1V8)

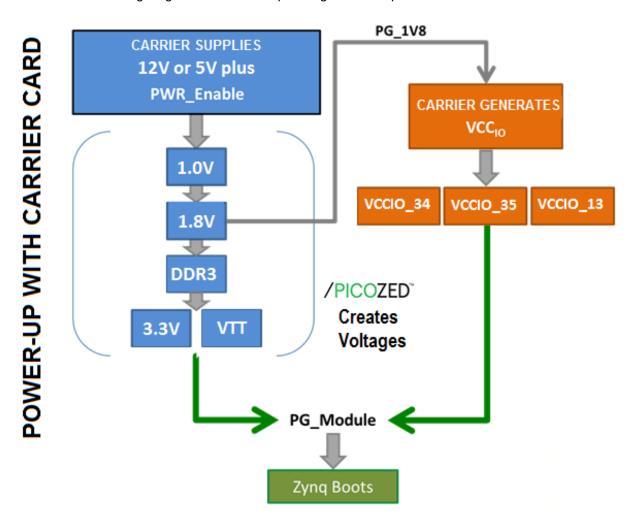

This circuit sequences power-up of PicoZed 7010/7020. 1.0V comes up first, then 1.8V, then VCCO\_DDR3 and then 3.3V. PG\_MODULE is connected to PS\_POR\_B on Zynq, thus when the power supplies are valid, PS\_POR\_B is released.

When the PicoZed 7010/7020 is mated to an end user carrier card, the POWER GOOD outputs of the end user carrier card should also be tied to the PG\_MODULE net on JX2.pin 11. If the end user carrier card power supplies do not have POWER GOOD outputs, a voltage supervisor or open-drain buffer should be used to complement this circuit.

PicoZed 7010/7020 also provides a power good signal to the end user carrier card to signal that Vccint and Vccaux are both up and the end user carrier card is free to bring up the Vcco supplies. This signal is called VCCIO\_EN (PG\_1V8) and is tied to JX2.pin 10.

**NOTE:** VCCIO\_EN is provided by the power good output of the 1.8V regulator.

The table below shows the maximum output current for each regulator on the PicoZed 7010/7020 System-On-Module.

| TI Part Number | Voltage (V) | Max Current (A) |

|----------------|-------------|-----------------|

| TLV62130       | 1.0         | 3               |

| TLV62130       | 1.8         | 3               |

| TLV62130       | 1.35        | 3               |

| TLV62130       | 3.3         | 3               |

| TPS51206       | 0.675       | 2               |

Table 16 - Voltage Rails w/ Max Output Current

#### 2.10.3 Power Supply Sequencing

When attached to an end user carrier card, the carrier card must provide an active-high, power enable signal, PWR\_ENABLE. This controls the first PicoZed 7010/7020 regulator (U19, 1.0V) turning on. This should be an open drain design such that this signal will float high (pulled high to 5V or 12V on PicoZed 7010/7020). This may allow for the special circumstance of the end user carrier card controlling the powering of the PicoZed 7010/7020 for low power applications.

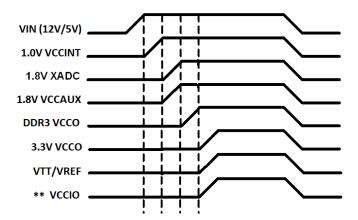

Sequencing for the power supplies follows the recommendations for the Zynq device. VCCINT/VCCPINT/VCCBRAM and VCCAUX/VCCPAUX supplies are tied together on the PicoZed 7010/7020 platform to create a low cost design. The following diagram illustrates the supply sequencing:

Figure 8 - Power Supply Sequencing

As noted above, if connected to an end user carrier card, the 1.8V power supply's power good output should is used as the enable to the VCCIO regulators via the PG\_1V8 (VCCIO\_EN) signal on the Micro Headers.